# Vita57 Quad SFP/SATA FMC Module User Manual

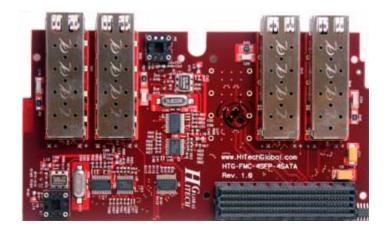

### HTG-FMC-X4SFP-X4SATA

Version 1.0 March 2010

Copyright © HiTech Global 2003-2010

#### **Disclaimer:**

HiTech Global does not assume any liability arising out of the application or use of any product described or shown herein; nor does it convey any license under its patents, copyrights, or mask work rights or any rights of others. HiTech Global reserves the right to make changes, at any time, in order to improve reliability and functionality of this product. HiTech Global will not assume responsibility for the use of any circuitry described herein other than circuitry entirely embodied in its products. HiTech Global provides any design, code, or information shown or described herein "as is." By providing the design, code, or information as one possible implementation of a feature, application, or standard, HiTech Global makes no representation that such implementation is free from any claims of infringement. End users are responsible for obtaining any rights they may require for their implementation. HiTech Global expressly disclaims any warranty whatsoever with respect to the adequacy of any such implementation, including but not limited to any warranties or representations that the implementation is free from claims of infringement, as well as any implied warranties of merchantability or fitness for a particular purpose.

HiTech Global will not assume any liability for the accuracy or correctness of any engineering or software support or assistance provided to a user. HiTech Global products are not intended for use in life support appliances, devices, or systems. Use of a HiTech Global product in such applications without the written consent of the appropriate HiTech Global officer is prohibited.

The contents of this manual are owned and copyrighted by HiTech Global Copyright. HiTech Global All Rights Reserved. Except as stated herein, none of the material may be copied, reproduced, distributed, republished, downloaded, displayed, posted, or transmitted in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of HiTech Global. Any unauthorized use of any material contained in this manual may violate copyright laws, trademark laws, the laws of privacy and publicity, and communications regulations and statutes.

#### **Revision History**

| Date      | Version | Notes       |

|-----------|---------|-------------|

| 3/12/2010 | 1.0     | Preliminary |

|           |         |             |

|           |         |             |

|           |         |             |

#### **Table of Contents:**

| 1   | Introduction                         | 4  |

|-----|--------------------------------------|----|

| 2   | Main Features                        | 4  |

| 3   | Components Placement                 | 5  |

| 4   | SFP Interface                        | 7  |

| 4.1 | Clock Generation for SFP Connectors  | 8  |

| 5   | SATA Interface                       | 11 |

| 5.1 | Clock Generation for SATA Connectors | 12 |

| 6   | FMC Interface                        | 15 |

#### 1) Introduction:

Vita 57 provides a mechanical standard for I/O mezzanine modules. This standard introduces a methodology that shall allow the front panel IO of IEEE 1101 form factor cards to be configured via mezzanine boards. Vita 57 modules have fixed locations for serial/parallel IOs, clocks, Jtag signals, VCC, and GND. HiTech Global's Vita 57 modules can be plugged into any Vita 57 based boards.

The FMC standard specifies Samtec's SEARAY<sup>TM</sup> connector set. The VITA 57 SEAM/SEAF Series system provides 400 I/Os in a 40 x 10 configuration or 160 I/Os in a selectively loaded 40 x 10 configuration, in 8.5mm and 10mm stack heights.

The Quad SFP/SATA FMC Module (HTG-FMC-X4SFP-X4SATA) is a FPGA Mezzanine Connector (FMC) daughter card with four SFP and FOUR Serial ATA (SATA) ports interfacing to total of 8 serial transceivers

#### 2) Main Features:

- Four SFP Connectors

- Four SATA Connectors

- EEPROM

- FMC Connector

- Dedicated on-board Super Clock for each interface

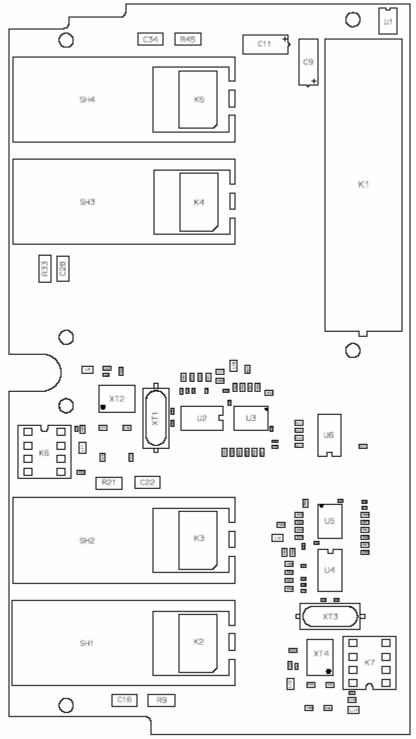

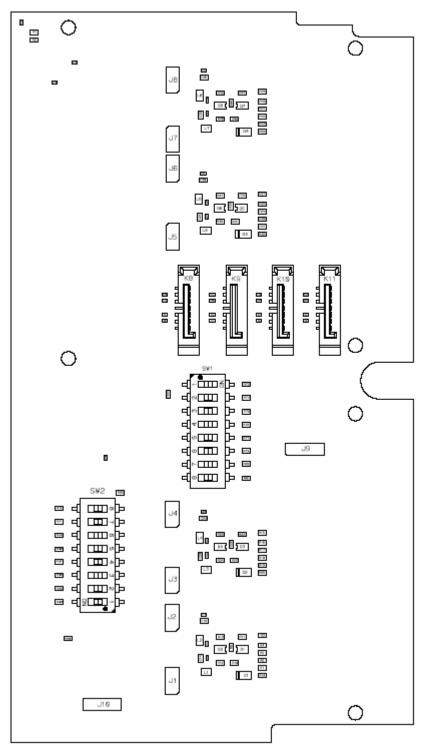

## 3) Components Placement

#### Figure (1): Primary Side

Figure (2): Secondary Side

#### 4) SFP Interface

Four SFP cages are connected to four Serial transceivers through the FMC connector (DP4-DP7)

| SFP0 "K2" Pin Name     | Signal Name | FMC Pin # | Note                                                             |

|------------------------|-------------|-----------|------------------------------------------------------------------|

| SFP_LOS                | LA01_CC_N   | D9        |                                                                  |

| SFP_TX_ENABLE          | LA00_CC_P   | G6        | J1: forced enable with no shunt,<br>controlled by FMC with shunt |

| SFP_RATESEL            | LA00_CC_N   | G7        | J2: forced full with no shunt, controlled by FMC with shunt      |

| SFP_TX_FAULT           | LA01_CC_P   | D8        |                                                                  |

| SFP_DETECT             | LA02_P      | H7        |                                                                  |

| SFP_SDA                | SDA_2       | C31       | Generated by I2C Multiplexer                                     |

| SFP_SCL                | SCL_2       | C30       | Generated by I2C Multiplexer                                     |

| SFP _TXP               | DP4_C2M_P   | A34       |                                                                  |

| SFP_TXN                | DP4_C2M_N   | A35       |                                                                  |

| SFP_ <mark>RX</mark> P | DP4_M2C_P   | A14       |                                                                  |

| SFP_RXN                | DP4_M2C_N   | A15       |                                                                  |

Tables (1-4) illustrate FMC pin assignment for the SFP ports.

Table (1): FMC Pin Assignment for SFP0 "K2"

| SFP1 "K3" Pin Name     | Signal Name | FMC Pin # | Notes                                                            |

|------------------------|-------------|-----------|------------------------------------------------------------------|

| SFP_LOS                | LA04_P      | H10       |                                                                  |

| SFP_TX_ENABLE          | LA02_N      | H8        | J3: forced enable with no shunt,<br>controlled by FMC with shunt |

| SFP_RATESEL            | LA03_P      | G9        | J4: forced full with no shunt, controlled by FMC with shunt      |

| SFP_TX_FAULT           | LA03_N      | G10       |                                                                  |

| SFP_DETECT             | LA04_N      | H11       |                                                                  |

| SFP_SDA                | SDA_3       | C31       | Generated by I2C Multiplexer                                     |

| SFP_SCL                | SCL_3       | C30       | Generated by I2C Multiplexer                                     |

| SFP _TXP               | DP5_C2M_P   | A38       |                                                                  |

| SFP_TXN                | DP5_C2M_N   | A39       |                                                                  |

| SFP_RXP                | DP5_M2C_P   | A18       |                                                                  |

| SFP_ <mark>RX</mark> N | DP5_M2C_N   | A19       |                                                                  |

Table (2): FMC Pin Assignment for SFP1 "K3"

| SFP2 "K4" Pin Name     | Signal Name | FMC Pin # | Notes                                                         |

|------------------------|-------------|-----------|---------------------------------------------------------------|

| SFP_LOS                | LA06_N      | C11       |                                                               |

| SFP_TX_ENABLE          | LA05_P      | D11       | J5: forced enable with no shunt, controlled by FMC with shunt |

| SFP_RATESEL            | LA05_N      | D12       | J6: forced full with no shunt, controlled by FMC with shunt   |

| SFP_TX_FAULT           | LA06_P      | C10       |                                                               |

| SFP_DETECT             | LA07_P      | H13       |                                                               |

| SFP_SDA                | SDA_4       | C31       | Generated by I2C Multiplexer                                  |

| SFP_SCL                | SCL_4       | C30       | Generated by I2C Multiplexer                                  |

| SFP _TXP               | DP6_C2M_P   | B36       |                                                               |

| SFP_TXN                | DP6_C2M_N   | B37       |                                                               |

| SFP_RXP                | DP6_M2C_P   | B16       |                                                               |

| SFP_ <mark>RX</mark> N | DP6_M2C_N   | B13       |                                                               |

#### Table (3): FMC Pin Assignment for SFP2 "K4"

| SFP3 "K5" Pin Name     | Signal Name | FMC Pin # | Notes                                                         |

|------------------------|-------------|-----------|---------------------------------------------------------------|

| SFP_LOS                | LA09_P      | D14       |                                                               |

| SFP_TX_ENABLE          | LA07_N      | H14       | J7: forced enable with no shunt, controlled by FMC with shunt |

| SFP_RATESEL            | LA08_P      | G12       | J8: forced full with no shunt, controlled by FMC with shunt   |

| SFP_TX_FAULT           | LA08_N      | G13       |                                                               |

| SFP_DETECT             | LA09_N      | D15       |                                                               |

| SFP_SDA                | SDA_5       | C31       | Generated by I2C Multiplexer                                  |

| SFP_SCL                | SCL_5       | C30       | Generated by I2C Multiplexer                                  |

| SFP <u>TX</u> P        | DP7_C2M_P   | B32       |                                                               |

| SFP_TXN                | DP7_C2M_N   | B33       |                                                               |

| SFP_ <mark>RX</mark> P | DP7_M2C_P   | B12       |                                                               |

| SFP_ <mark>RX</mark> N | DP7_M2C_N   | B13       |                                                               |

| Table (4) | FMC | Pin | Assignment | for | SFP3 | "K5" |

|-----------|-----|-----|------------|-----|------|------|

|-----------|-----|-----|------------|-----|------|------|

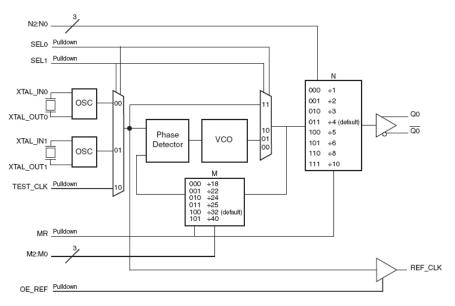

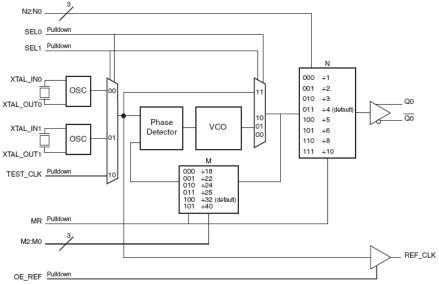

#### **4.1) Clock Generation for SFP Connectors**

Clock generation circuit for the SFP connectors uses the following components (all 4 ports share the same clock)

- Socket (K7) for user oscillator of choice TEST\_CLK

- Very low-jitter 25 MHz Silicon Lab Si570 Oscillator (XT4) XTAL\_IN1

- 25 MHz Crystal (XT3) XTAL\_IN0 and XTAL\_OUT0

- ICS843001-21 (U4) low phase noise LVPECL Frequency Synthesizer

- DIFFERENTIAL-TO-LVDS FANOUT BUFFER (U5)

The Si570 XO utilizes Silicon Laboratories' advanced DSPLL® circuitry to provide a low-jitter clock at any frequency. The Si570 is user-programmable to any output frequency from 10 to 945 MHz and select frequencies to 1400 MHz with <1 ppb resolution. The device is programmed via an I2C serial interface. Unlike traditional XO/VCXOs where a different crystal is required for each output frequency, the Si57x uses one fixed frequency crystal and a DSPLL clock synthesis IC to provide any-rate frequency operation. This IC-based approach allows the crystal resonator to provide exceptional frequency stability and reliability.

ICS843001-2 is a highly versatile, low phase noise LVPECL Synthesizer which can generate low jitter reference clocks for a variety of communications applications and is a member of the HiPerClocksTM family of high performance clock solutions from IDT. The dual crystal interface allows the synthesizer to support up to two communications standards in a given application (i.e. 1GB Ethernet with a 25MHz crystal and 1Gb Fibre Channel using a 26.5625MHz crystal). The rms phase jitter performance is typically less than 1ps, thus making the device acceptable for use in demanding applications such as OC48 SONET and 10Gb Ethernet.

**Figure (3): Frequency Synthesizer Block Diagram**

Table (5) illustrates common configurations for different industry standard applications. Depending on value of the input frequency (through socket or on-board oscillators), "M", and "N" divider values users can generate different output frequencies.

\*\*\* Example for generating 125 MHz by using a 25 MHz oscillator:

Output frequency = (25MHz) \* (25) / 5 = 625/5 = 125 MHz

| Input Reference<br>Clock (MHz) | M Divider<br>Value | N Divider<br>Value | VCO (MHz) | Output<br>Frequency<br>(MHz) | Application          |

|--------------------------------|--------------------|--------------------|-----------|------------------------------|----------------------|

| 27                             | 22                 | 8                  | 594       | 74.25                        | HDTV                 |

| 24.75                          | 24                 | 8                  | 594       | 74.25                        | HDTV                 |

| 14.8351649                     | 40                 | 8                  | 593.4066  | 74.1758245                   | HDTV                 |

| 19.44                          | 32                 | 4                  | 622.08    | 155.52                       | SONET                |

| 19.44                          | 32                 | 8                  | 622.08    | 77.76                        | SONET                |

| 19.44                          | 32                 | 1                  | 622.08    | 622.08                       | SONET                |

| 19.44                          | 32                 | 2                  | 622.08    | 311.04                       | SONET                |

| 19.53125                       | 32                 | 4                  | 625       | 156.25                       | 10 GigE              |

| 25                             | 25                 | 4                  | 625       | 156.25                       | 10 GigE              |

| 25                             | 25                 | 5                  | 625       | 125                          | 1 GigE               |

| 25                             | 25                 | 10                 | 625       | 62.5                         | 1 GigE               |

| 25                             | 24                 | 6                  | 600       | 100                          | PCI Express          |

| 25                             | 24                 | 4                  | 600       | 150                          | SATA                 |

| 25                             | 24                 | 8                  | 600       | 75                           | SATA                 |

| 26.5625                        | 24                 | 6                  | 637.5     | 106.25                       | Fibre Channel 1      |

| 26.5625                        | 24                 | 3                  | 637.5     | 212.5                        | 4 Gig Fibre Channel  |

| 26.5625                        | 24                 | 4                  | 637.5     | 159.375                      | 10 Gig Fibre Channel |

| 31.25                          | 18                 | 5                  | 562.5     | 187.5                        | 12 GigE              |

Table (5) Frequency Synthesizer Common Configuration Table

Table (6), (7), and (8) illustrate selection of "M", "N", and "Clock Source". Table (9) illustrates SW2 Dip Switch setting based on selected values of the above mentioned parameters.

| Inputs |      |   |                    | iency (MHz) |         |

|--------|------|---|--------------------|-------------|---------|

| M2     | <br> |   | M Divider<br>Value | Minimum     | Maximum |

| 0      | 0    | 0 | 18                 | 31.1        | 38.9    |

| 0      | 0    | 1 | 22                 | 25.5        | 31.8    |

| 0      | 1    | 0 | 24                 | 23.3        | 29.2    |

| 0      | 1    | 1 | 25                 | 22.4        | 28.0    |

| 1      | 0    | 0 | 32                 | 17.5        | 21.9    |

| 1      | 0    | 1 | 40                 | 14.0        | 17.5    |

Table (6) Frequency Synthesizer Programmable "M" Output Divider Function Table

|    | Inputs |    |                 |

|----|--------|----|-----------------|

| N2 | N1     | NO | M Divider Value |

| 0  | 0      | 0  | 1               |

| 0  | 0      | 1  | 2               |

| 0  | 1      | 0  | 3               |

| 0  | 1      | 1  | 4               |

| 1  | 0      | 0  | 5               |

| 1  | 0      | 1  | 6               |

| 1  | 1      | 0  | 8               |

| 1  | 1      | 1  | 10              |

Table (7) Frequency Synthesizer Programmable "N" Output Divider Function Table

| Inputs |      |           |          |

|--------|------|-----------|----------|

| SEL1   | SELO | Reference | PLL Mode |

| 0      | 0    | XTAL0     | 1        |

| 0      | 1    | XTAL1     | 2        |

| 1      | 0    | TEST_CLK  | 8        |

| 1      | 1    | TEST_CLK1 | 10       |

|   | DinSwitch           | ICS<br>Conf.Pin | Logic     | State      |  |

|---|---------------------|-----------------|-----------|------------|--|

| ۱ | DipSwitch<br>Number | Name            | DipSw. ON | DipSw. OFF |  |

|   | 1                   | N0              | 0         | 1          |  |

|   | 2                   | N1              | 0         | 1          |  |

| 3 | 3                   | N2              | 0         | 1          |  |

|   | 4                   | MO              | 0         | 1          |  |

|   | 5                   | M1              | 0         | 1          |  |

|   | 6                   | M2              | 0         | 1          |  |

|   | 7                   | SEL0            | 0         | 1          |  |

|   | 8                   | SEL1            | 0         | 1          |  |

Table (9) Frequency Synthesizer SW2 DIP Switch Setting

#### 5) SATA Interface

Four SATA ports are connected to four Serial transceivers through the FMC connectors (DP0-DP3)

Tables (10-13) illustrate FMC pin assignment for the SATA ports.

| SATA0 "K8" Pin Name       | Signal Name | FMC Pin # | Note |

|---------------------------|-------------|-----------|------|

| SATA0 _TXP                | DP0_C2M_P   | C2        |      |

| SATA0 _TXN                | DP0_C2M_N   | C3        |      |

| SATA0 <u>RX</u> P         | DP0_M2C_P   | C6        |      |

| SATA0 _ <mark>RX</mark> N | DP0_M2C_N   | C7        |      |

Table (10): FMC Pin Assignment for SATA "K8"

| SATA1 "K9" Pin Name | Signal Name | FMC Pin # | Note |

|---------------------|-------------|-----------|------|

| SATA1 _TXP          | DP1_C2M_P   | A22       |      |

| SATA1 _TXN          | DP1_C2M_N   | A23       |      |

| SATA1 <u>RX</u> P   | DP1_M2C_P   | A2        |      |

| SATA1 _RXN          | DP1_M2C_N   | A3        |      |

#### Table (11): FMC Pin Assignment for SATA "K9"

| SATA2 "K10" Pin Name      | Signal Name | FMC Pin # | Note |

|---------------------------|-------------|-----------|------|

| SATA2 _TXP                | DP2_C2M_P   | A26       |      |

| SATA2 _TXN                | DP2_C2M_N   | A27       |      |

| SATA2 <u>RXP</u>          | DP2_M2C_P   | A6        |      |

| SATA2 _ <mark>RX</mark> N | DP2_M2C_N   | A7        |      |

#### Table (12): FMC Pin Assignment for SATA "K10"

| SATA3 "K11" Pin Name      | Signal Name | FMC Pin # | Note |

|---------------------------|-------------|-----------|------|

| SATA3 _TXP                | DP3_C2M_P   | A30       |      |

| SATA3 _TXN                | DP3_C2M_N   | A31       |      |

| SATA3 <u>RX</u> P         | DP3_M2C_P   | A10       |      |

| SATA3 _ <mark>RX</mark> N | DP3_M2C_N   | A11       |      |

#### Table (13): FMC Pin Assignment for SATA "K11"

#### **5.1) Clock Generation for SATA Connectors**

Clock generation circuit for the SATA connectors uses the following components (all 4 ports share the same clock)

- Socket (K6) for user oscillator of choice TEST\_CLK

- Very low-jitter 25 MHz Silicon Lab Si570 Oscillator (XT2) XTAL\_IN1

- 25 MHz Crystal (XT1) XTAL\_IN0 and XTAL\_OUT0

- ICS843001-21 (U2) low phase noise LVPECL Frequency Synthesizer

- DIFFERENTIAL-TO-LVDS FANOUT BUFFER (U3)

The Si570 XO utilizes Silicon Laboratories' advanced DSPLL® circuitry to provide a low-jitter clock at any frequency. The Si570 is user-programmable to any output frequency from 10 to 945 MHz and select frequencies to 1400 MHz with <1 ppb resolution. The device is programmed via an I2C serial interface. Unlike traditional XO/VCXOs where a different crystal is required for each output frequency, the Si57x uses one fixed frequency crystal and a DSPLL clock synthesis IC to provide any-rate frequency operation. This IC-based approach allows the crystal resonator to provide exceptional frequency stability and reliability.

ICS843001-2 is a highly versatile, low phase noise LVPECL Synthesizer which can generate low jitter reference clocks for a variety of communications applications and is a member of the HiPerClocksTM family of high performance clock solutions from IDT. The dual crystal interface allows the synthesizer to support up to two communications standards in a given application (i.e.

1GB Ethernet with a 25MHz crystal and 1Gb Fibre Channel using a 26.5625MHz crystal). The rms phase jitter performance is typically less than 1ps, thus making the device acceptable for use in demanding applications such as OC48 SONET and 10Gb Ethernet.

Figure (4): Frequency Synthesizer Block Diagram

Table (14) illustrates common configurations for different industry standard applications. Depending on value of the input frequency (through socket or on-board oscillators), "M", and "N" divider values users can generate different output frequencies.

| Output frequency = $(25 \text{MHz}) * (24) / 4 = 600/4 = 150 \text{ MHz}$ |                    |                    |           |                              |                      |  |  |

|---------------------------------------------------------------------------|--------------------|--------------------|-----------|------------------------------|----------------------|--|--|

| Input Reference<br>Clock (MHz)                                            | M Divider<br>Value | N Divider<br>Value | VCO (MHz) | Output<br>Frequency<br>(MHz) | Application          |  |  |

| 27                                                                        | 22                 | 8                  | 594       | 74.25                        | HDTV                 |  |  |

| 24.75                                                                     | 24                 | 8                  | 594       | 74.25                        | HDTV                 |  |  |

| 14.8351649                                                                | 40                 | 8                  | 593.4066  | 74.1758245                   | HDTV                 |  |  |

| 19.44                                                                     | 32                 | 4                  | 622.08    | 155.52                       | SONET                |  |  |

| 19.44                                                                     | 32                 | 8                  | 622.08    | 77.76                        | SONET                |  |  |

| 19.44                                                                     | 32                 | 1                  | 622.08    | 622.08                       | SONET                |  |  |

| 19.44                                                                     | 32                 | 2                  | 622.08    | 311.04                       | SONET                |  |  |

| 19.53125                                                                  | 32                 | 4                  | 625       | 156.25                       | 10 GigE              |  |  |

| 25                                                                        | 25                 | 4                  | 625       | 156.25                       | 10 GigE              |  |  |

| 25                                                                        | 25                 | 5                  | 625       | 125                          | 1 GigE               |  |  |

| 25                                                                        | 25                 | 10                 | 625       | 62.5                         | 1 GigE               |  |  |

| 25                                                                        | 24                 | 6                  | 600       | 100                          | PCI Express          |  |  |

| 25                                                                        | 24                 | 4                  | 600       | 150                          | SATA                 |  |  |

| 25                                                                        | 24                 | 8                  | 600       | 75                           | SATA                 |  |  |

| 26.5625                                                                   | 24                 | 6                  | 637.5     | 106.25                       | Fibre Channel 1      |  |  |

| 26.5625                                                                   | 24                 | 3                  | 637.5     | 212.5                        | 4 Gig Fibre Channel  |  |  |

| 26.5625                                                                   | 24                 | 4                  | 637.5     | 159.375                      | 10 Gig Fibre Channel |  |  |

| 31.25                                                                     | 18                 | 5                  | 562.5     | 187.5                        | 12 GigE              |  |  |

\*\*\* Example for generating 150 MHz by using a 25 MHz oscillator:

**Table (14) Frequency Synthesizer Common Configuration Table**

|    | Inputs |      |                    | Input Frequency (MHz) |         |  |

|----|--------|------|--------------------|-----------------------|---------|--|

| M2 | <br>   | <br> | M Divider<br>Value | Minimum               | Maximum |  |

| 0  | 0      | 0    | 18                 | 31.1                  | 38.9    |  |

| 0  | 0      | 1    | 22                 | 25.5                  | 31.8    |  |

| 0  | 1      | 0    | 24                 | 23.3                  | 29.2    |  |

| 0  | 1      | 1    | 25                 | 22.4                  | 28.0    |  |

| 1  | 0      | 0    | 32                 | 17.5                  | 21.9    |  |

| 1  | 0      | 1    | 40                 | 14.0                  | 17.5    |  |

Table (15), (16), and (17) illustrate selection of "M", "N", and "Clock Source". Table (18) illustrates SW1 Dip Switch setting based on selected values of the above mentioned parameters.

Table (15) Frequency Synthesizer Programmable "M" Output Divider Function Table

|    | Inputs |    |                 |

|----|--------|----|-----------------|

| N2 | N1     | NO | M Divider Value |

| 0  | 0      | 0  | 1               |

| 0  | 0      | 1  | 2               |

| 0  | 1      | 0  | 3               |

| 0  | 1      | 1  | 4               |

| 1  | 0      | 0  | 5               |

| 1  | 0      | 1  | 6               |

| 1  | 1      | 0  | 8               |

| 1  | 1      | 1  | 10              |

1

1

10

Table (16) Frequency Synthesizer Programmable "N" Output Divider Function Table

| Inputs |      |           |          |  |

|--------|------|-----------|----------|--|

| SEL1   | SEL0 | Reference | PLL Mode |  |

| 0      | 0    | XTAL0     | 1        |  |

| 0      | 1    | XTAL1     | 2        |  |

| 1      | 0    | TEST_CLK  | 8        |  |

| 1      | 1    | TEST_CLK1 | 10       |  |

Table (17) Frequency Synthesizer Bypass Mode Function Table

|   | DipSwitch | ICS<br>Conf.Pin | Logic State |            |

|---|-----------|-----------------|-------------|------------|

| ١ | Number    | Name            | DipSw. ON   | DipSw. OFF |

|   | 1         | N0              | 0           | 1          |

|   | 2         | N1              | 0           | 1          |

| 3 | 3         | N2              | 0           | 1          |

|   | 4         | MO              | 0           | 1          |

| 6 | 5         | M1              | 0           | 1          |

|   | 6         | M2              | 0           | 1          |

|   | 7         | SEL0            | 0           | 1          |

|   | 8         | SEL1            | 0           | 1          |

Table (18) Frequency Synthesizer SW1 DIP Switch Setting

#### 6) FMC Interface

The SFP+ Module is populated with a 400-pin <u>Samtec connector</u> for implementation of <u>Vita 57</u> FPGA Mezzanine Card (FMC) interface. The Vita57 calls for fixed location of IOs, Power, Clocks, and JTAG signals so any compliant module can easily be pluggable into any compliant carrier card.

The FMC connector provides access to 8 Serial Transceivers (on the FPGA side) JTAG signals, 12V/3.3V/Adjustable supplies, I2C signals, and multiple differential clocks.

Table (19) and (20) illustrate the pin assignment for the FMC connector interface.

| к            | J          | н             | G             | F         | Е         | D             | с             | в             | А         |

|--------------|------------|---------------|---------------|-----------|-----------|---------------|---------------|---------------|-----------|

| VREF_B_M2C   | GND        | VREF_A_M2C    | GND           | PG_M2C    | GND       | PG_C2M        | GND           | RES1          | GND       |

| 2 GND        | CLK3 M2C P | PRSNT M2C L   | CLK1 M2C P    | GND       | HA01 P CC | GND           | DP0 C2M P     | GND           | DP1 M2C P |

| 3 GND        | CLK3_M2C_N | GND           | CLK1_M2C_N    | GND       | HA01_N_CC | GND           | DP0_C2M_N     | GND           | DP1_M2C_N |

| 4 CLK2_M2C_P | GND        | CLK0_M2C_P    | GND           | HA00_P_CC | GND       | GBTCLK0_M2C_P | GND           | DP9_M2C_P     | GND       |

| 5 CLK2_M2C_N | GND        | CLK0_M2C_N    | GND           | HA00_N_CC | GND       | GBTCLK0_M2C_N | GND           | DP9_M2C_N     | GND       |

| 6 GND        | HA03 P     | GND           | LA00 P CC     | GND       | HA05 P    | GND           | DP0 M2C P     | GND           | DP2 M2C P |

| 7 HA02_P     | HA03_N     | LA02_P        | LA00_N_CC     | HA04_P    | HA05_N    | GND           | DP0_M2C_N     | GND           | DP2_M2C_N |

| 8 HA02_N     | GND        | LA02_N        | GND           | HA04_N    | GND       | LA01_P_CC     | GND           | DP8_M2C_P     | GND       |

| 9 GND        | HA07_P     | GND           | LA03_P        | GND       | HA09_P    | LA01_N_CC     | GND           | DP8_M2C_N     | GND       |

| 10 HA06_P    | HA07_N     | LA04_P        | LA03_N        | HA08_P    | HA09_N    | GND           | LA06_P        | GND           | DP3_M2C_P |

| 11 HA06_N    | GND        | LA04_N        | GND           | HA08_N    | GND       | LA05_P        | LA06_N        | GND           | DP3_M2C_N |

| 12 GND       | HA11_P     | GND           | LA08_P        | GND       | HA13_P    | LA05_N        | GND           | DP7_M2C_P     | GND       |

| 13 HA10_P    | HA11_N     | LA07_P        | LA08_N        | HA12_P    | HA13_N    | GND           | GND           | DP7_M2C_N     | GND       |

| 14 HA10_N    | GND        | LA07_N        | GND           | HA12_N    | GND       | LA09_P        | LA10_P        | GND           | DP4_M2C_P |

| 15 GND       | HA 14_P    | GND           | LA12_P        | GND       | HA16_P    | LA09_N        | LA10_N        | GND           | DP4_M2C_N |

| 16 HA17_P_CC | HA14_N     | LA11_P        | LA12_N        | HA15_P    | HA16_N    | GND           | GND           | DP6_M2C_P     | GND       |

| 17 HA17_N_CC | GND        | LA11_N        | GND           | HA15_N    | GND       | LA13_P        | GND           | DP6_M2C_N     | GND       |

| 18 GND       | HA 18_P    | GND           | LA16_P        | GND       | HA20_P    | LA13_N        | LA 14_P       | GND           | DP5_M2C_P |

| 19 HA21_P    | HA18_N     | LA15_P        | LA16_N        | HA19_P    | HA20_N    | GND           | LA14_N        | GND           | DP5_M2C_N |

| 20 HA21 N    | GND        | LA15 N        | GND           | HA19 N    | GND       | LA17 P CC     | GND           | GBTCLK1 M2C P | GND       |

| 21 GND       | HA22_P     | GND           | LA20_P        | GND       | HB03_P    | LA17_N_CC     | GND           | GBTCLK1_M2C_N | GND       |

| 22 HA23_P    | HA22_N     | LA19_P        | LA20_N        | HB02_P    | HB03_N    | GND           | LA18_P_CC     | GND           | DP1_C2M_P |

| 23 HA23_N    | GND        | LA19_N        | GND           | HB02_N    | GND       | LA23_P        | LA18_N_CC     | GND           | DP1_C2M_N |

| 24 GND       | HB01_P     | GND           | LA22_P        | GND       | HB05_P    | LA23_N        | GND           | DP9_C2M_P     | GND       |

| 25 HB00_P_CC | HB01_N     | LA21_P        | LA22_N        | HB04_P    | HB05_N    | GND           | GND           | DP9_C2M_N     | GND       |

| 26 HB00_N_CC | GND        | LA21_N        | GND           | HB04_N    | GND       | LA26_P        | LA27_P        | GND           | DP2_C2M_P |

| 27 GND       | HB07_P     | GND           | LA25_P        | GND       | HB09_P    | LA26_N        | LA27_N        | GND           | DP2_C2M_N |

| 28 HB06_P_CC | HB07_N     | LA24_P        | LA25_N        | HB08_P    | HB09_N    | GND           | GND           | DP8_C2M_P     | GND       |

| 29 HB06_N_CC | GND        | LA24_N        | GND           | HB08_N    | GND       | TCK           | GND           | DP8_C2M_N     | GND       |

| 30 GND       | HB11_P     | GND           | LA29_P        | GND       | HB13_P    | TDI           | SCL           | GND           | DP3_C2M_P |

| 31 HB10_P    | HB11_N     | LA28_P        | LA29_N        | HB12_P    | HB13_N    | TDO           | SDA           | GND           | DP3_C2M_N |

| 32 HB10_N    | GND        | LA28_N        | GND           | HB12_N    | GND       | 3P3VAUX       | GND           | DP7_C2M_P     | GND       |

| 33 GND       | HB15 P     | GND           | LA31 P        | GND       | HB19 P    | TMS           | GND           | DP7 C2M N     | GND       |

| 34 HB14_P    | HB15_N     | LA30_P        | LA31_N        | HB16_P    | HB19_N    | TRST_L        | GA0           | GND           | DP4_C2M_P |

| 35 HB14_N    | GND        | LA30_N        | GND           | HB16_N    | GND       | GA1           | 12P0V         | GND           | DP4_C2M_N |

| 36 GND       | HB18 P     | GND           | LA33 P        | GND       | HB21 P    | 3P3V          | GND           | DP6 C2M P     | GND       |

| 37 HB17_P_CC | HB18_N     | LA32_P        | LA33_N        | HB20_P    | HB21_N    | GND           | 12P0V         | DP6_C2M_N     | GND       |

| 38 HB17_N_CC | GND        | LA32_N        | GND           | HB20_N    | GND       | 3P3V          | GND           | GND           | DP5_C2M_P |

| 39 GND       | VIO B M2C  | GND           | VADJ          | GND       | VADJ      | GND           | 3P3V          | GND           | DP5 C2M N |

| 40 VIO_B_M2C | GND        | VADJ          | GND           | VADJ      | GND       | 3P3V          | GND           | RES0          | GND       |

|              |            | LPC Connector | LPC Connector |           |           | LPC Connector | LPC Connector |               |           |

Table (19):

FMC Pin Assignment

|    | Column "B"    |                 |       |    | Column "A"      |                 |       |

|----|---------------|-----------------|-------|----|-----------------|-----------------|-------|

|    | FMC Pin Name  | Pin Description | DEST. |    | FMC Pin<br>Name | Pin Description | DEST. |

| 1  | RES1          | Reserved        |       | 1  | GND             | -               |       |

| 2  | GND           | -               |       | 2  | DP1_M2C_P       | SATA1 RXDATA_P  |       |

| 3  | GND           | -               |       | 3  | DP1_M2C_N       | SATA1 RXDATA_N  |       |

| 4  | DP9_M2C_P     | NC              |       | 4  | GND             | -               |       |

| 5  | DP9_M2C_N     | NC              |       | 5  | GND             | -               |       |

| 6  | GND           | -               |       | 6  | DP2_M2C_P       | SATA2 RXDATA_P  |       |

| 7  | GND           | -               |       | 7  | DP2_M2C_N       | SATA2 RXDATA_N  |       |

| 8  | DP8_M2C_P     | NC              |       | 8  | GND             | -               |       |

| 9  | DP8_M2C_N     | NC              |       | 9  | GND             | -               |       |

| 10 | GND           | -               |       | 10 | DP3_M2C_P       | SATA3 RXDATA_P  |       |

| 11 | GND           | -               |       | 11 | DP3_M2C_N       | SATA3 RXDATA_N  |       |

| 12 | DP7_M2C_P     | SFP3 RXDATA_P   |       | 12 | GND             | -               |       |

| 13 | DP7_M2C_N     | SFP3 RXDATA_N   |       | 13 | GND             | -               |       |

| 14 | GND           | -               |       | 14 | DP4_M2C_P       | SFP0 RXDATA_P   |       |

| 15 | GND           | -               |       | 15 | DP4_M2C_N       | SFP0 RXDATA_N   |       |

| 16 | DP6_M2C_P     | SFP2 RXDATA_P   |       | 16 | GND             | -               |       |

| 17 | DP6_M2C_N     | SFP2 RXDATA_N   |       | 17 | GND             | -               |       |

| 18 | GND           | -               |       | 18 | DP5_M2C_P       | SFP1 RXDATA_P   |       |

| 18 | GND           | -               |       | 18 | DP5_M2C_N       | SFP1 RXDATA_N   |       |

| 20 | GBTCLK1_M2C_P | SFP_REF_CLK1_P  |       | 20 | GND             | -               |       |

| 21 | GBTCLK1_M2C_N | SFP_REF_CLK1_P  |       | 21 | GND             | -               |       |

| 22 | GND           | -               |       | 22 | DP1_C2M_P       | SATA1TXDATA_P   |       |

| 23 | GND           | -               |       | 23 | DP1_C2M_N       | SATA1 TXDATA_N  |       |

| 24 | DP9_C2M_P     | NC              | NC    | 24 | GND             | -               |       |

| 25 | DP9_C2M_N     | NC              | NC    | 25 | GND             | -               |       |

| 26 | GND           | -               |       | 26 | DP2_C2M_P       | SATA2 TXDATA_P  |       |

| 27 | GND           | -               |       | 27 | DP2_C2M_N       | SATA2 TXDATA_N  |       |

| 28 | DP8_C2M_P     | NC              | NC    | 28 | GND             | -               |       |

| 29 | DP8_C2M_N     | NC              | NC    | 29 | GND             | -               |       |

| 30 | GND           | -               |       | 30 | DP3_C2M_P       | SATA3 TXDATA_P  |       |

| 31 | GND           | -               |       | 31 | DP3_C2M_N       | SATA3 TXDATA_N  |       |

| 32 | DP7_C2M_P     | SFP3 TXDATA_P   |       | 32 | GND             | -               |       |

| 33 | DP7_C2M_N     | SFP3 TXDATA_N   |       | 33 | GND             | -               |       |

| 34 | GND           | -               |       | 34 | DP4_C2M_P       | SFP0 TXDATA_P   |       |

| 35 | GND           | -               |       | 35 | DP4_C2M_N       | SFP0 TXDATA_N   |       |

| 36 | DP6_C2M_P     | SFP2 TXDATA_P   |       | 36 | GND             | -               |       |

| 37 | DP6_C2M_N     | SFP2 TXDATA_N   |       | 37 | GND             | -               |       |

| 38 | GND           | -               |       | 38 | DP5_C2M_P       | SFP1 TXDATA_P   |       |

| 39 | GND           | -               |       | 39 | DP5_C2M_N       | SFP1TXDATA_N    |       |

| 40 | RES0          | NC              |       | 40 | GND             | -               |       |

|    | Column "D"    |                      |       |    | Column "C"      |                      |       |

|----|---------------|----------------------|-------|----|-----------------|----------------------|-------|

|    | FMC Pin Name  | Pin Description      | DEST. |    | FMC Pin<br>Name | Pin Description      | DEST. |

| 1  | PG_C2M        | Power Good           |       | 1  | GND             | NC                   |       |

| 2  | GND           |                      |       | 2  | DP0_C2M_P       | SATA0 TXDATA_P       |       |

| 3  | GND           |                      |       | 3  | DP0_C2M_N       | SATA0 TXDATA_N       |       |

| 4  | GBTCLK0_M2C_P | SATA_REF_CLK_P       |       | 4  | GND             |                      |       |

| 5  | GBTCLK0_M2C_N | SATA_REF_CLK_P       |       | 5  | GND             |                      |       |

| 6  | GND           |                      |       | 6  | DP0_M2C_P       | SATA0 RXDATA_P       |       |

| 7  | GND           |                      |       | 7  | DP0_M2C_N       | SATA0 RXDATA_N       |       |

| 8  | LA01_P_CC     | User defined signal  | NC    | 8  | GND             |                      |       |

| 9  | LA01_N_CC     | User defined signal  | NC    | 9  | GND             |                      |       |

| 10 | GND           |                      |       | 10 | LA06_P          |                      | NC    |

| 11 | LA05_P        | User defined signal  | NC    | 11 | LA06_N          |                      | NC    |

| 12 | LA05_N        | User defined signal  | NC    | 12 | GND             |                      |       |

| 13 | GND           |                      |       | 13 | GND             |                      |       |

| 14 | LA09_P        | User defined signal  | NC    | 14 | LA10_P          |                      | NC    |

| 15 | LA09_N        | User defined signal  | NC    | 15 | LA10_N          |                      | NC    |

| 16 | GND           |                      |       | 16 | GND             |                      |       |

| 17 | LA13_P        | User defined signal  | NC    | 17 | GND             |                      |       |

| 18 | LA13_N        | User defined signal  | NC    | 18 | LA14_P          |                      | NC    |

| 18 | GND           |                      |       | 18 | LA14_N          |                      | NC    |

| 20 | LA17_P_CC     | User defined signal  | NC    | 20 | GND             |                      |       |

| 21 | LA17_N_CC     | User defined signal  | NC    | 21 | GND             |                      |       |

| 22 | GND           |                      |       | 22 | LA18_P_CC       |                      | NC    |

| 23 | LA23_P        | User defined signal  | NC    | 23 | LA18_N_CC       |                      | NC    |

| 24 | LA23_N        | User defined signal  | NC    | 24 | GND             |                      |       |

| 25 | GND           |                      |       | 25 | GND             |                      |       |

| 26 | LA26_P        | User defined signal  | NC    | 26 | LA27_P          |                      | NC    |

| 27 | LA26_N        | User defined signal  | NC    | 27 | LA27_N          |                      | NC    |

| 28 | GND           |                      |       | 28 | GND             |                      |       |

| 29 | TCK           | JTAG                 |       | 29 | GND             |                      |       |

| 30 | TDI           | JTAG BYPASS          |       | 30 | SCL             | I2C serial clock.    |       |

| 31 | TDO           | JTAG                 |       | 31 | SDA             | I2C serial data.     |       |

| 32 | 3P3VAUX       | 3.3V Aux. Supply     | 3.3V  | 32 | GND             | -                    | -     |

| 33 | TMS           | JTAG                 |       | 33 | GND             | -                    | -     |

| 34 | TRST_L        | Asynch. Init.        |       | 34 | GA0             | Geographical address |       |

| 35 | GA1           | Geographical address | U5-2  | 35 | 12P0V           | 12V Supply           |       |

| 36 | 3P3V          | 3.3V Supply          | 3.3V  | 36 | GND             |                      |       |

| 37 | GND           |                      | GND   | 37 | 12P0V           | 12V Supply           |       |

| 38 | 3P3V          | 3.3V Supply          | 3.3V  | 38 | GND             |                      |       |

| 39 | GND           |                      | GND   | 39 | 3P3V            | 3.3V Supply          |       |

| 40 | 3P3V          | 3.3V Supply          | 3.3V  | 40 | GND             |                      |       |

#### Column "F" Column "E" FMC Pin FMC Pin Name **Pin Description** DEST. **Pin Description** DEST. Name Power Good 1 1 PG\_M2C GND GND GND 2 2 User defined signal NC GND GND GND HA01\_P\_CC 3 3 User defined signal NC GND GND HA01\_N\_CC GND 4 HA00\_P\_CC User defined signal NC 4 GND GND GND User defined signal 5 5 NC HA00\_N\_CC GND GND GND 6 GND GND 6 HA05\_P User defined signal NC GND User defined signal NC 7 User defined signal NC 7 HA05\_N HA04\_P 8 User defined signal NC 8 HA04\_N GND GND GND 9 9 User defined signal NC GND GND GND HA09\_P 10 User defined signal NC 10 User defined signal NC HA08\_P HA09\_N User defined signal NC 11 HA08\_N 11 GND GND GND 12 12 User defined signal NC GND GND GND HA13\_P NC 13 User defined signal NC 13 User defined signal HA12\_P HA13\_N 14 User defined signal NC 14 GND HA12\_N GND GND 15 15 User defined signal NC GND GND GND HA16\_P NC 16 User defined signal NC 16 User defined signal HA16\_N HA15\_P 17 User defined signal NC 17 GND GND HA15\_N GND 18 18 User defined signal NC GND GND HA20\_P GND 18 User defined signal NC 18 User defined signal NC HA19\_P HA20\_N 20 User defined signal NC 20 GND GND HA19\_N GND 21 21 User defined signal NC GND GND GND HB03\_P User defined signal NC User defined signal NC 22 22 HB02\_P HB03\_N 23 User defined signal NC 23 HB02\_N GND GND GND 24 24 User defined signal NC GND GND GND HB05\_P 25 User defined signal NC 25 User defined signal NC HB05\_N HB04\_P User defined signal 26 NC 26 HB04\_N GND GND GND 27 27 User defined signal NC GND GND GND HB09 P NC 28 User defined signal NC 28 User defined signal HB08\_P HB09\_N 29 User defined signal NC 29 HB08\_N GND GND GND 30 30 User defined signal NC GND GND GND HB13\_P 31 User defined signal NC 31 User defined signal NC HB12\_P HB13\_N 32 User defined signal NC 32 HB12\_N GND GND GND 33 33 User defined signal NC GND GND GND HB19\_P 34 User defined signal NC 34 User defined signal NC HB16\_P HB19\_N 35 User defined signal NC 35 HB16\_N GND GND GND 36 36 User defined signal NC GND GND GND HB21\_P 37 User defined signal NC 37 User defined signal NC HB20\_P HB21\_N 38 User defined signal NC 38 HB20\_N GND GND GND 39 39 Adjustable Voltage GND GND GND VADJ

### Quad SFP/SATA FMC Module – User Manual

40

VADJ

40

GND

GND

GND

Adjustable Voltage

|    | Column "H"   |                     |       |    | Column "G"      |                     |       |

|----|--------------|---------------------|-------|----|-----------------|---------------------|-------|

|    | FMC Pin Name | Pin Description     | DEST. |    | FMC Pin<br>Name | Pin Description     | DEST. |

| 1  | VREF_A_M2C   | Reference voltage   |       | 1  | GND             | GND                 | GND   |

| 2  | PRSNT_M2C_L  | Present Signal      |       | 2  | CLK1_M2C_P      | Differential Clock  | NC    |

| 3  | GND          | GND                 | GND   | 3  | CLK1_M2C_N      | Differential Clock  | NC    |

| 4  | CLK0_M2C_P   | Differential Clock  | NC    | 4  | GND             | GND                 | GND   |

| 5  | CLK0_M2C_N   | Differential Clock  | NC    | 5  | GND             | GND                 | GND   |

| 6  | GND          | GND                 | GND   | 6  | LA00_P_CC       | User defined signal | NC    |

| 7  | LA02_P       | User defined signal | NC    | 7  | LA00_N_CC       | User defined signal | NC    |

| 8  | LA02_N       | User defined signal | NC    | 8  | GND             | GND                 | GND   |

| 9  | GND          | GND                 | GND   | 9  | LA03_P          | User defined signal | NC    |

| 10 | LA04_P       | User defined signal | NC    | 10 | LA03_N          | User defined signal | NC    |

| 11 | LA04_N       | User defined signal | NC    | 11 | GND             | GND                 | GND   |

| 12 | GND          | GND                 | GND   | 12 | LA08_P          | User defined signal | NC    |

| 13 | LA07_P       | User defined signal | NC    | 13 | LA08_N          | User defined signal | NC    |

| 14 | LA07_N       | User defined signal | NC    | 14 | GND             | GND                 | GND   |

| 15 | GND          | GND                 | GND   | 15 | LA12_P          | User defined signal | NC    |

| 16 | LA11_P       | User defined signal | NC    | 16 | LA12_N          | User defined signal | NC    |

| 17 | LA11_N       | User defined signal | NC    | 17 | GND             | GND                 | GND   |

| 18 | GND          | GND                 | GND   | 18 | LA16_P          | User defined signal | NC    |

| 18 | LA15_P       | User defined signal | NC    | 18 | LA16_N          | User defined signal | NC    |

| 20 | LA15_N       | User defined signal | NC    | 20 | GND             | GND                 | GND   |

| 21 | GND          | GND                 | GND   | 21 | LA20_P          | User defined signal | NC    |

| 22 | LA19_P       | User defined signal | NC    | 22 | LA20_N          | User defined signal | NC    |

| 23 | LA19_N       | User defined signal | NC    | 23 | GND             | GND                 | GND   |

| 24 | GND          | GND                 | GND   | 24 | LA22_P          | User defined signal | NC    |

| 25 | LA21_P       | User defined signal | NC    | 25 | LA22_N          | User defined signal | NC    |

| 26 | LA21_N       | User defined signal | NC    | 26 | GND             | GND                 | GND   |

| 27 | GND          | GND                 | GND   | 27 | LA25_P          | User defined signal | NC    |

| 28 | LA24_P       | User defined signal | NC    | 28 | LA25_N          | User defined signal | NC    |

| 29 | LA24_N       | User defined signal | NC    | 29 | GND             | GND                 | GND   |

| 30 | GND          | GND                 | GND   | 30 | LA29_P          | User defined signal | NC    |

| 31 | LA28_P       | User defined signal | NC    | 31 | LA29_N          | User defined signal | NC    |

| 32 | LA28_N       | User defined signal | NC    | 32 | GND             | GND                 | GND   |

| 33 | GND          | GND                 | GND   | 33 | LA31_P          | User defined signal | NC    |

| 34 | LA30_P       | User defined signal | NC    | 34 | LA31_N          | User defined signal | NC    |

| 35 | LA30_N       | User defined signal | NC    | 35 | GND             | GND                 | GND   |

| 36 | GND          | GND                 | GND   | 36 | LA33_P          | User defined signal | NC    |

| 37 | LA32_P       | User defined signal | NC    | 37 | LA33_N          | User defined signal | NC    |

| 38 | LA32_N       | User defined signal | NC    | 38 | GND             | GND                 | GND   |

| 39 | GND          | GND                 | GND   | 39 | VADJ            | Adjustable Voltage  |       |

| 40 | VADJ         | Adjustable Voltage  |       | 40 | GND             |                     |       |

|    | Column "K"   |                     |       |    | Column "J"      |                     |       |

|----|--------------|---------------------|-------|----|-----------------|---------------------|-------|

|    | FMC Pin Name | Pin Description     | DEST. |    | FMC Pin<br>Name | Pin Description     | DEST. |

| 1  | VREF_B_M2C   | Reference voltage   |       | 1  | GND             | GND                 | GND   |

| 2  | GND          | GND                 | GND   | 2  | CLK3_M2C_P      | Differential Clock  | NC    |

| 3  | GND          | GND                 | GND   | 3  | CLK3_M2C_N      | Differential Clock  | NC    |

| 4  | CLK2_M2C_P   | Differential Clock  | NC    | 4  | GND             | GND                 | GND   |

| 5  | CLK2_M2C_N   | Differential Clock  | NC    | 5  | GND             | GND                 | GND   |

| 6  | GND          | GND                 | GND   | 6  | HA03_P          | User defined signal | NC    |

| 7  | HA02_P       | User defined signal | NC    | 7  | HA03_N          | User defined signal | NC    |

| 8  | HA02_N       | User defined signal | NC    | 8  | GND             | GND                 | GND   |

| 9  | GND          | GND                 | GND   | 9  | HA07_P          | User defined signal | NC    |

| 10 | HA06_P       | User defined signal | NC    | 10 | HA07_N          | User defined signal | NC    |

| 11 | HA06_N       | User defined signal | NC    | 11 | GND             | GND                 | GND   |

| 12 | GND          | GND                 | GND   | 12 | HA11_P          | User defined signal | NC    |

| 13 | HA10_P       | User defined signal | NC    | 13 | HA11_N          | User defined signal | NC    |

| 14 | HA10_N       | User defined signal | NC    | 14 | GND             | GND                 | GND   |

| 15 | GND          | GND                 | GND   | 15 | HA14_P          | User defined signal | NC    |

| 16 | HA17_P_CC    | User defined signal | NC    | 16 | HA14_N          | User defined signal | NC    |

| 17 | HA17_N_CC    | User defined signal | NC    | 17 | GND             | GND                 | GND   |

| 18 | GND          | GND                 | GND   | 18 | HA18_P          | User defined signal | NC    |

| 18 | HA21_P       | User defined signal | NC    | 18 | HA18_N          | User defined signal | NC    |

| 20 | HA21_N       | User defined signal | NC    | 20 | GND             | GND                 | GND   |

| 21 | GND          | GND                 | GND   | 21 | HA22_P          | User defined signal | NC    |

| 22 | HA23_P       | User defined signal | NC    | 22 | HA22_N          | User defined signal | NC    |

| 23 | HA23_N       | User defined signal | NC    | 23 | GND             | GND                 | GND   |

| 24 | GND          | GND                 | GND   | 24 | HB01_P          | User defined signal | NC    |

| 25 | HB00_P_CC    | User defined signal | NC    | 25 | HB01_N          | User defined signal | NC    |

| 26 | HB00_N_CC    | User defined signal | NC    | 26 | GND             | GND                 | GND   |

| 27 | GND          | GND                 | GND   | 27 | HB07_P          | User defined signal | NC    |

| 28 | HB06_P_CC    | User defined signal | NC    | 28 | HB07_N          | User defined signal | NC    |

| 29 | HB06_N_CC    | User defined signal | NC    | 29 | GND             | GND                 | GND   |

| 30 | GND          | GND                 | GND   | 30 | HB11_P          | User defined signal | NC    |

| 31 | HB10_P       | User defined signal | NC    | 31 | HB11_N          | User defined signal | NC    |

| 32 | HB10_N       | User defined signal | NC    | 32 | GND             | GND                 | GND   |

| 33 | GND          | GND                 | GND   | 33 | HB15_P          | User defined signal | NC    |

| 34 | HB14_P       | User defined signal | NC    | 34 | HB15_N          | User defined signal | NC    |

| 35 | HB14_N       | User defined signal | NC    | 35 | GND             | GND                 | GND   |

| 36 | GND          | GND                 | GND   | 36 | HB18_P          | User defined signal | NC    |

| 37 | HB17_P_CC    | User defined signal | NC    | 37 | HB18_N          | User defined signal | NC    |

| 38 | HB17_N_CC    | User defined signal | NC    | 38 | GND             | GND                 | GND   |

| 39 | GND          | GND                 | GND   | 39 | VIO_B_M2C       | IO Bank Voltage     |       |

| 40 | VIO_B_M2C    | IO Bank Voltage     |       | 40 | GND             |                     |       |

Table (20): FMC Pin Assignment