Order

### AFE4300

SBAS586C - JUNE 2012 - REVISED SEPTEMBER 2017

# AFE4300 Low-Cost, Integrated Analog Front-End for Weight-Scale and Body Composition Measurement

## Features

- Weight-Scale Front-End:

- Supports up to Four Load Cell Inputs

- On-Chip Load Cell 1.7-V Excitation Voltage for **Ratiometric Measurement**

- 68-nVrms Input-Referred Noise (0.1 Hz to 2 Hz)

- Best-Fit Linearity: 0.01% of Full-Scale

- Weight-Scale Measurement : 540 µA

- Body Composition Front-End:

- Supports Up To Three Tetra-Polar Complex Impedance Measurements

- 6-Bit, 1-MSPS Sine-Wave Generation Digitalto-Analog Converter (DAC)

- 247.5-µArms, ±20% Excitation Source

- 0.1-Ω Measurement RMS Noise in 2-Hz BW

- Body Composition Measurement : 970 µA

- Analog-to-Digital Converter (ADC):

- 16 Bits, 860 SPS

- Supply Current: 110 µA

## 2 Applications

Weight Scales With Body Composition Measurements

## **3** Description

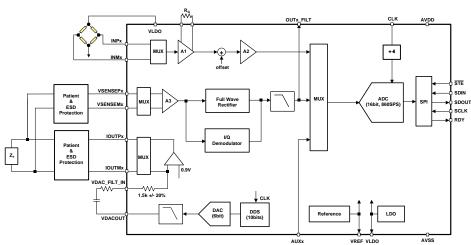

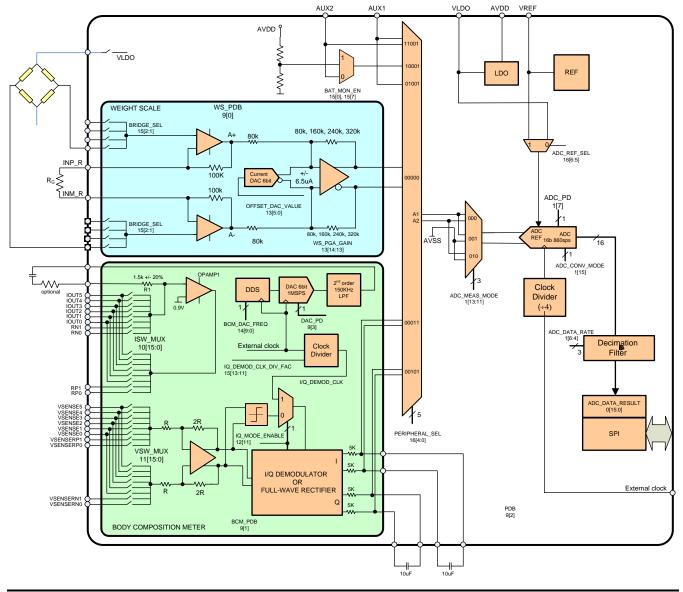

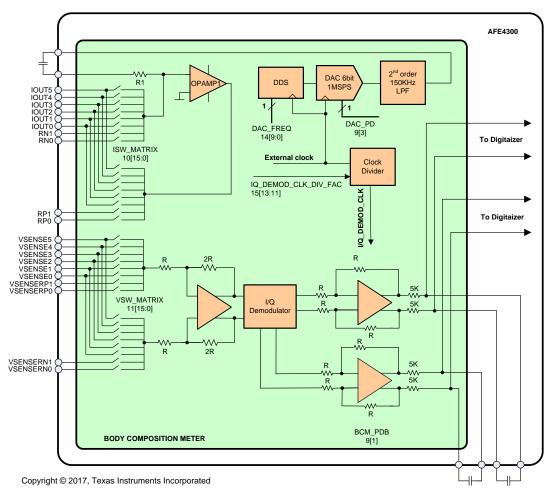

The AFE4300 is a low-cost analog front-end incorporating two separate signal chains: one chain for weight-scale (WS) measurement and the other for body composition measurement (BCM) analysis. A 16-bit, 860-SPS analog-to-digital converter (ADC) is multiplexed between both chains. The weight measurement chain includes an instrumentation amplifier (INA) with the gain set by an external resistor, followed by a 6-bit digital-to-analog converter (DAC) for offset correction, and a circuit to drive the external bridge/load cell with a fixed 1.7 V for ratiometric measurements.

The AFE4300 can also measure body composition by applying a sinusoidal current into the body. The sinusoidal current is generated with an internal pattern generator and a 6-bit, 1-MSPS DAC. A voltage-to-current converter applies this sinusoidal current into the body, between two terminals. The voltage created across these two terminals as a result of the impedance of the body is measured back with a differential amplifier, rectified, and the amplitude is extracted and measured by the 16-bit ADC.

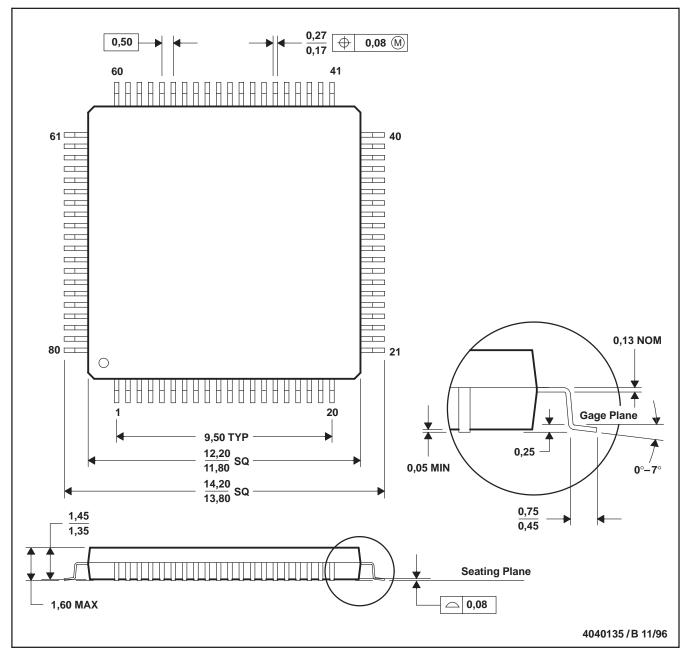

The AFE4300 operates from 2 V to 3.6 V, is specified from 0°C to +70°C, and is available in a LQFP-80 package.

### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)     |

|-------------|-----------|---------------------|

| AFE4300     | LQFP (80) | 12.00 mm × 12.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

## **Functional Block Diagram**

# **Table of Contents**

| 1 | Fea  | tures 1                                                                             |

|---|------|-------------------------------------------------------------------------------------|

| 2 | Арр  | lications1                                                                          |

| 3 | Des  | cription1                                                                           |

| 4 | Rev  | ision History 2                                                                     |

| 5 | Pin  | Configuration and Functions 4                                                       |

| 6 | Spe  | cifications                                                                         |

|   | 6.1  | Absolute Maximum Ratings 6                                                          |

|   | 6.2  | ESD Ratings 6                                                                       |

|   | 6.3  | Recommended Operating Conditions 6                                                  |

|   | 6.4  | Thermal Information 6                                                               |

|   | 6.5  | Electrical Characteristics: Front-End Amplification<br>(Weight-Scale Signal Chain)7 |

|   | 6.6  | Electrical Characteristics: Body Composition<br>Measurement Front-End               |

|   | 6.7  | Electrical Characteristics: Analog-to-Digital<br>Converter                          |

|   | 6.8  | Electrical Characteristics: Digital Input/Output9                                   |

|   | 6.9  | Timing Requirements: Serial Interface Timing 10                                     |

|   | 6.10 | Typical Characteristics 11                                                          |

| 7 | Deta | ailed Description 12                                                                |

|   | 7.1  | Overview 12                                                                         |

|    | 7.2  | Functional Block Diagram                        | 12 |

|----|------|-------------------------------------------------|----|

|    | 7.3  | Feature Description                             | 13 |

|    | 7.4  | Device Functional Modes                         | 20 |

|    | 7.5  | Programming                                     | 21 |

|    | 7.6  | Register Maps                                   | 23 |

| 8  | App  | lication and Implementation                     | 30 |

|    | 8.1  | Application Information                         | 30 |

|    | 8.2  | Typical Application                             | 32 |

| 9  | Pow  | er Supply Recommendations                       | 34 |

|    | 9.1  | Power-Supply Recommendation and Initialization  | 34 |

| 10 | Lay  | out                                             | 35 |

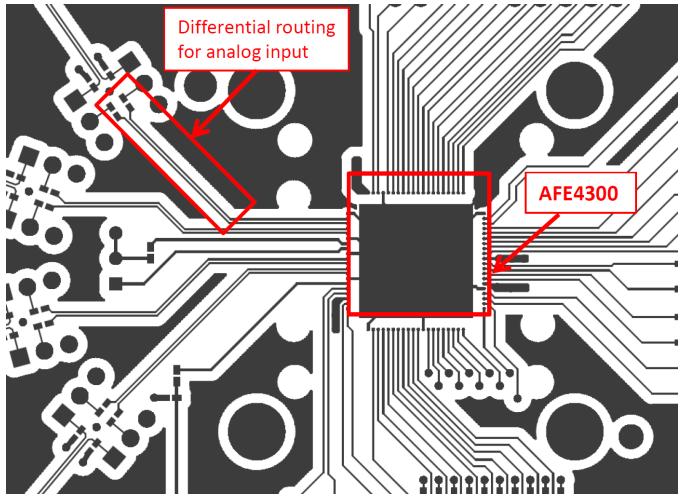

|    | 10.1 | Layout Guidelines                               | 35 |

|    | 10.2 | Layout Example                                  | 35 |

| 11 | Dev  | ice and Documentation Support                   | 36 |

|    | 11.1 | Receiving Notification of Documentation Updates | 36 |

|    | 11.2 | Community Resources                             | 36 |

|    | 11.3 | Trademarks                                      | 36 |

|    | 11.4 | Electrostatic Discharge Caution                 | 36 |

|    | 11.5 | Glossary                                        | 36 |

| 12 | Mec  | hanical, Packaging, and Orderable               |    |

|    |      | mation                                          | 36 |

|    |      |                                                 |    |

# 4 Revision History

2

Submit Documentation Feedback

### Changes from Revision B (June 2013) to Revision C

| • | Added Device Information table, ESD Ratings table, Feature Description section, Device Functional Modes section,<br>Programming section, Application and Implementation section, Power Supply Recommendations section, Layout<br>section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section | 1   |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| • | Changed Body Composition Features bullet: changed 375 to 247.5 in Excitation Source sub-bullet and deleted<br>Dynamic Range sub-bullet                                                                                                                                                                                                           |     |

| • | Changed TQFP to LQFP throughout document                                                                                                                                                                                                                                                                                                         |     |

| • | Deleted Package Information section                                                                                                                                                                                                                                                                                                              | . 4 |

| • | Changed Pin Functions table title                                                                                                                                                                                                                                                                                                                | . 4 |

| • | Changed clock to serial clock in SCLK pin description of Pin Functions table                                                                                                                                                                                                                                                                     | 5   |

| • | Changed VSENSEN to VSENSEM in pins 41 and 42 in Pin Functions table                                                                                                                                                                                                                                                                              | 5   |

| • | Changed AVSS parameter name to Ground from Supply voltage in Recommended Operating Conditions table                                                                                                                                                                                                                                              | 6   |

| • | Changed symbol R1 to R <sub>FB1</sub> in Electrical Characteristics: Front-End Amplification (Weight-Scale Signal Chain) table                                                                                                                                                                                                                   | 7   |

| • | Changed typical specification of DAC full-scale voltage parameter from 1 to 1.05 in Electrical Characteristics: Body<br>Composition Measurement Front-End table                                                                                                                                                                                  | 8   |

| • | Changed Electrical Characteristics: Digital Input/Output table title                                                                                                                                                                                                                                                                             | 9   |

| • | Changed multiplication signs (x) to minimum and maximum specifications of <i>Electrical Characteristics: Digital</i><br>Input/Output table                                                                                                                                                                                                       | 9   |

| • | Changed x-axis unit from µArms to µApk in BCM DAC Output Current Distribution figure                                                                                                                                                                                                                                                             | 11  |

| • | Changed Functional Block Diagram: swapped positions of RP1, RP0 and RN1, RN0 pins                                                                                                                                                                                                                                                                | 12  |

| • | Changed BCM in AC Rectifier Mode figure: swapped positions of RP1, RP0 and RN1, RN0 pins                                                                                                                                                                                                                                                         | 15  |

| • | Changed AC Rectification section: changed images to high-frequency images in second paragraph, VDAC to VDACOUT in Equation 5, and changed third paragraph                                                                                                                                                                                        | 16  |

| • | Changed third paragraph of AC Rectification section: deleted (still within the 500-µArms limit) from fourth sentence, changed last sentence.                                                                                                                                                                                                     | 16  |

| • | Changed BCM in I/Q Demodulator Mode figure: swapped positions of RP1, RP0 and RN1, RN0 pins                                                                                                                                                                                                                                                      | 17  |

www.ti.com

Page

## **Revision History (continued)**

| • | Changed Operating Modes section                                                                                                                                                                                                   | . 20 |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| • | Changed <i>negative input</i> to <i>output</i> in descriptions of IOUTP[5:0] and RP[1:0] and <i>output</i> to <i>negative input</i> in descriptions of IOUTN[5:0] and RN[1:0] in ISW_MUX register                                 | 26   |

| • | Changed bit 9 to DAC9 from 0 in BCM_DAC_FREQ register and changed bit count in bit descriptions to reflect this change                                                                                                            | 27   |

| • | Changed f <sub>CLK</sub> = 1 MHz to f <sub>CLK</sub> = 1.024 MHz in BCM_DAC_FREQ register                                                                                                                                         | . 27 |

| • | Changed Component Values Corresponding to Figure 12 table: changed title of second column from Suggested Value to Illustrative Value, R3, R4 illustrative value to 10 k $\Omega$ from 100 k $\Omega$ , and changed table footnote | 30   |

| • | Changed 1 MHz to 1.024 MHz in Example Value column of Weight Scale Design Requirements table                                                                                                                                      | 32   |

| • | Deleted touch from list of possible power-up interrupts in third paragraph of Detailed Design Procedure section                                                                                                                   | 33   |

| • | Changed first sentence of Application Curve section to reference Figure 15                                                                                                                                                        | 33   |

| • | Changed capacitor to capacitances in last bullet of Layout Guidelines section                                                                                                                                                     | 35   |

### Changes from Revision A (June 2012) to Revision B

## Page

| • | Changed title condition for Electrical Charancteristics                 | . 7 |

|---|-------------------------------------------------------------------------|-----|

| • | Changed test condition for rectifier bandwidth parameter                | . 8 |

| • | Changed y-axis unit in Figure 5                                         | 11  |

| • | Changed R1 percentage in Functional Block Diagram                       | 12  |

| • | Changed feedback resistor percentage in second paragraph after Figure 6 | 13  |

| • | Changed description for last row of Table 2                             | 23  |

| • | Changed bit descriptions of ISW_MUX register                            | 26  |

| • | Changed bit 9 for BCM_DAC_FREQ (Address 0x0E)                           | 27  |

| • | Changed bit numbers for MISC_REGISTER3 (Address 0x1A)                   | 29  |

|   |                                                                         | —   |

## Changes from Original (June 2012) to Revision A

Page

Changed data sheet from product preview to production data ......1

Texas

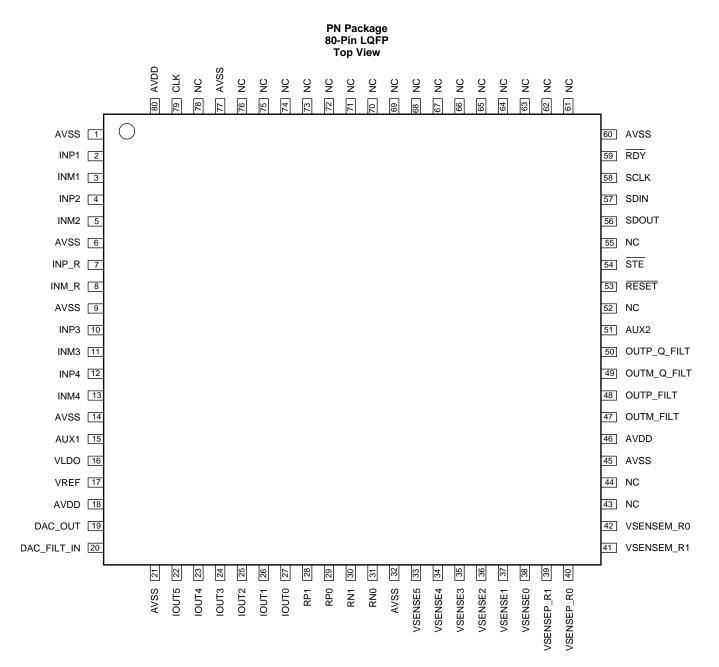

## 5 Pin Configuration and Functions

### **Pin Functions**

| PIN         |                                 |     |                                                                                     |  |  |

|-------------|---------------------------------|-----|-------------------------------------------------------------------------------------|--|--|

| NAME NUMBER |                                 | I/O | DESCRIPTION                                                                         |  |  |

| AAUX1       | 15                              | I   | Auxiliary input to the ADC                                                          |  |  |

| AAUX2       | 51                              | I   | Auxiliary input to the ADC                                                          |  |  |

| AVDD        | 18, 46, 80                      | _   | Supply (3.3 V)                                                                      |  |  |

| AVSS        | 1, 6, 9, 14, 21, 32, 45, 60, 77 | —   | Ground                                                                              |  |  |

| CLK         | 79                              | I   | 1-MHz clock                                                                         |  |  |

| DAC_FILT_IN | 20                              | I   | Current generator input. Connect ac blocking capacitor between this pin and pin 19. |  |  |

| DACOUT      | 19                              | 0   | DAC output. Connect ac blocking capacitor between this pin and pin 20.              |  |  |

INSTRUMENTS

## Pin Functions (continued)

| PIN NAME NUMBER |                           |          | DESCRIPTION                                                                     |  |  |

|-----------------|---------------------------|----------|---------------------------------------------------------------------------------|--|--|

|                 |                           | I/O      |                                                                                 |  |  |

| INM1            | 3                         |          |                                                                                 |  |  |

| INM2            | 5                         |          |                                                                                 |  |  |

| INM3            | 11                        |          |                                                                                 |  |  |

| INM4            | 13                        |          | Instrumentation amplifier differential inputs for each of the four weight-scale |  |  |

| INP1            | 2                         | - 1      | channels                                                                        |  |  |

| INP2            | 4                         |          |                                                                                 |  |  |

| INP3            | 10                        |          |                                                                                 |  |  |

| INP4            | 12                        |          |                                                                                 |  |  |

| INM_R           | 8                         | _        |                                                                                 |  |  |

| INP_R           | 7                         | _        | Connection of gain setting resistor for the instrumentation amplifier           |  |  |

| IOUT0           | 27                        |          |                                                                                 |  |  |

| IOUT1           | 26                        |          |                                                                                 |  |  |

| IOUT2           | 25                        |          |                                                                                 |  |  |

| IOUT3           | 24                        | 0        | Current source output to electrodes                                             |  |  |

| IOUT4           | 23                        |          |                                                                                 |  |  |

| IOUT5           | 22                        |          |                                                                                 |  |  |

| NC              | 43, 44, 52, 55, 61-76, 78 | _        | Do not connect                                                                  |  |  |

| OUTM_I_FILT     | 47                        |          |                                                                                 |  |  |

| OUTP_I_FILT     | 48                        |          | I channel demodulator low pass filter, connect 10 $\mu F$ between both pins     |  |  |

| OUTM_Q_FILT     | 49                        |          |                                                                                 |  |  |

| OUTP_Q_FILT     | 50                        |          | Q channel demodulator low pass filter, connect 10 µF between both pins          |  |  |

| RDY             | 59                        | 0        | Data ready                                                                      |  |  |

| RN0             | 31                        |          |                                                                                 |  |  |

| RN1             | 30                        |          |                                                                                 |  |  |

| RP0             | 29                        | 0        | Current source output to calibration resistors                                  |  |  |

| RP1             | 28                        |          |                                                                                 |  |  |

| RST             | 53                        | I        | Reset. 0: reset, 1: normal operation.                                           |  |  |

| SCLK            | 58                        | I        | Serial clock to latch input data (negative edge latch)                          |  |  |

| SDIN            | 57                        | I        | Serial data input                                                               |  |  |

| SDOUT           | 56                        | 0        | Serial data output                                                              |  |  |

| STE             | 54                        | I        | SPI enable. 0: shift data in, 1: disable.                                       |  |  |

| VLDO            | 16                        | 0        | LDO output to supply the bridges (~1.7 V), connect 470 nF to AVSS               |  |  |

| VREF            | 17                        | 0        | Reference voltage (connect 470 nF to AVSS)                                      |  |  |

| VSENSEM_R0      | 42                        |          |                                                                                 |  |  |

| VSENSEM_R1      | 41                        | <b>.</b> |                                                                                 |  |  |

| VSENSEP_R0      | 40                        | - 1      | Input to differential amplifier from calibration resistors                      |  |  |

| VSENSEP_R1      | 39                        | 7        |                                                                                 |  |  |

| VSENSE0         | 38                        |          |                                                                                 |  |  |

| VSENSE1         | 37                        |          |                                                                                 |  |  |

| VSENSE2         | 36                        |          | Insuit to differential emplifier from electrod-                                 |  |  |

| VSENSE3         | 35                        | - I      | Input to differential amplifier from electrode                                  |  |  |

| VSENSE4         | 34                        |          |                                                                                 |  |  |

| VSENSE5         | 33                        |          |                                                                                 |  |  |

## 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                            |              | MIN  | MAX        | UNIT |

|------------------------------------------------------------|--------------|------|------------|------|

| Voltage range                                              | AVDD to AVSS | -0.3 | 4.1        | V    |

|                                                            | Any pin      | -0.3 | AVDD + 0.3 |      |

| Diode current at any device pin                            |              |      | ±2         | mA   |

| Maximum operating junction temperature, T <sub>J</sub> max |              |      | 105        | °C   |

| Storage humidity                                           |              | 10%  | 90%        | Rh   |

| Storage temperature, T <sub>stg</sub>                      |              | -25  | 85         | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                         |                                                                                | VALUE                   | UNIT                                                                                            |

|-------------------------|--------------------------------------------------------------------------------|-------------------------|-------------------------------------------------------------------------------------------------|

| Flastrastatia disabarga | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2000                   | V                                                                                               |

| Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±1000                   | v                                                                                               |

|                         | Electrostatic discharge                                                        | Electrostatic discharge | Electrostatic discharge Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> ±2000 |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                  |                                | MIN | NOM | MAX | UNIT |

|------------------|--------------------------------|-----|-----|-----|------|

| AVDD             | Supply voltage                 | 2   |     | 3.6 | V    |

| AVSS             | Ground                         |     | 0   |     | V    |

| f <sub>CLK</sub> | External clock input frequency |     | 1   |     | MHz  |

| T <sub>A</sub>   | Ambient temperature range      | 0   |     | 70  | °C   |

### 6.4 Thermal Information

|                       |                                              | AFE4300   |      |

|-----------------------|----------------------------------------------|-----------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | PN (LQFP) | UNIT |

|                       |                                              | 80 PINS   |      |

| $R_{\thetaJA}$        | Junction-to-ambient thermal resistance       | 50.5      | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 14.2      | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 25.3      | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 0.5       | °C/W |

| Ψјв                   | Junction-to-board characterization parameter | 24.9      | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | N/A       | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 6.5 Electrical Characteristics: Front-End Amplification (Weight-Scale Signal Chain)

over operating free-air temperature range, AVDD – AVSS = 3 V, G1 = 183, and G2 = 1 (unless otherwise noted)

|                     |                                        |                                              | А          |                        |     |                        |  |

|---------------------|----------------------------------------|----------------------------------------------|------------|------------------------|-----|------------------------|--|

|                     | PARAMETER                              | TEST CONDITIONS                              | MIN        | TYP                    | MAX | UNIT                   |  |

| BRIDGE S            | SUPPLY                                 |                                              |            |                        | 1   |                        |  |

| V <sub>(VLDO)</sub> | Output voltage (bridge supply voltage) |                                              |            | 1.7                    |     | V                      |  |

|                     | Output aurorat                         | Current capability                           |            |                        | 20  | mA                     |  |

| lo                  | Output current                         | Short-circuit protection                     |            | 100                    |     | mA                     |  |

| t <sub>STBY</sub>   | Enable, disable time                   | With 470-nF capacitor on the VLDO pin        |            | 1                      |     | ms                     |  |

| AMPLIFIC            | ATION CHAIN                            |                                              |            |                        |     |                        |  |

|                     | Offset error                           | With offset correction DAC disabled          |            | 80                     |     | μV                     |  |

|                     | Offset drift vs temperature            | With offset correction DAC disabled          |            | 0.25                   |     | μV/°C                  |  |

|                     | Input bias current                     |                                              |            | ±70                    |     | fA                     |  |

|                     | Input offset current                   |                                              |            | ±140                   |     | fA                     |  |

| V <sub>n</sub>      | Noise voltage, equivalent input        | G1 = 183, 0.01 Hz < f < 2 Hz                 |            | 68                     |     | nVrms                  |  |

| l <sub>n</sub>      | Noise current, equivalent input        | f = 10 Hz                                    |            | 100                    |     | fA/√Hz                 |  |

| z <sub>id</sub>     | Differential input impedance           |                                              |            | 100    4               |     | $G\Omega \parallel pF$ |  |

| z <sub>ic</sub>     | Common-mode input impedance            |                                              |            | 100    8               |     | GΩ    pF               |  |

| CMRR                | Input common-mode rejection ratio      | G1 = 183                                     |            | 95                     |     | dB                     |  |

| INL <sub>WS</sub>   | Gain nonlinearity                      | From input to digital output (including ADC) |            | 0.01                   |     | % of FS <sup>(1)</sup> |  |

|                     | First-stage gain equation              |                                              | (1 + 2 × 1 | 00k / R <sub>G</sub> ) |     | V/V                    |  |

| t <sub>up</sub>     | Power-up time                          | From power up to valid reading               |            | 1                      |     | ms                     |  |

| R <sub>FB1</sub>    | Internal feedback resistors            |                                              | 95         | 100                    | 105 | kΩ                     |  |

| Gain2               | Second-stage gain settings             |                                              |            | 1, 2, 3, 4             |     |                        |  |

|                     | Total gain error                       |                                              |            | ±5%                    |     |                        |  |

|                     | Offset DAC number of bits              |                                              |            | 6                      |     | Bits                   |  |

| I <sub>DAC</sub>    | Full-scale offset DAC output current   |                                              |            | ±6.5                   |     | μA                     |  |

(1) FS = full-scale.

SBAS586C -JUNE 2012-REVISED SEPTEMBER 2017

www.ti.com

NSTRUMENTS

**EXAS**

# 6.6 Electrical Characteristics: Body Composition Measurement Front-End

over operating free-air temperature range, AVDD – AVSSS = 3 V (unless otherwise noted)

|                     |                                                  |                                                                        | AFE43 | 00      |                   |

|---------------------|--------------------------------------------------|------------------------------------------------------------------------|-------|---------|-------------------|

|                     | PARAMETER                                        | TEST CONDITIONS                                                        | MIN   | TYP MAX | UNIT              |

| WAVEFOR             | M GENERATOR                                      |                                                                        |       |         |                   |

|                     | DAC resolution                                   |                                                                        |       | 6       | Bits              |

|                     | DAC full-scale voltage                           | Common-mode voltage = 0.9 V                                            |       | 1.05    | V <sub>(PP)</sub> |

|                     | DAC sample rate                                  |                                                                        |       | 1       | MSPS              |

| $BW_{LPF}$          | -3 dB bandwidth of the 2nd-order low-pass filter |                                                                        | 150   | ±30     | kHz               |

| R1                  | Internal current-setting resistor                |                                                                        | 1.5 ± | 20%     | kΩ                |

| DEMODUL             | ATION CHAIN                                      |                                                                        |       |         |                   |

|                     | Input Impedance                                  |                                                                        |       | 50      | kΩ                |

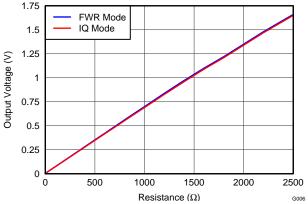

|                     | Gain                                             | From impedance to dc output of demodulator, IQ mode and FWR mode       |       | 0.72    | V/kΩ              |

|                     | Gain error (without calibration)                 | FWR mode and I/Q mode                                                  |       | 2.5     | % of FS           |

|                     | Offset error (without calibration)               | FWR mode and I/Q mode                                                  |       | ±5      | mV                |

| CMRR                | Common-mode rejection ratio                      |                                                                        |       | 75      | dB                |

|                     | No. lin o site                                   | 0-Ω to 1.25-kΩ range                                                   |       | 0.15    | % of FS           |

|                     | Nonlinearity                                     | 0-Ω to 2.50-kΩ range                                                   |       | 3       | % of FS           |

| BW <sub>DEMOD</sub> | Rectifier bandwidth                              | Internal resistor = 5 k $\Omega$ ,<br>external capacitor = 4.7 $\mu$ F | 3.5 ± | 20%     | Hz                |

|                     | Output noise at rectifier output                 | 20-kHz waveform, noise integrated from 0.01 Hz to 2 Hz                 |       | 15      | µVrms             |

## 6.7 Electrical Characteristics: Analog-to-Digital Converter

over operating free-air temperature range, AVDD - AVSS = 3 V (unless otherwise noted)

|                      |                                     |                                     | AF              | E4300                |     |      |

|----------------------|-------------------------------------|-------------------------------------|-----------------|----------------------|-----|------|

|                      | PARAMETER                           | TEST CONDITIONS                     | MIN             | TYP                  | MAX | UNIT |

| ANALOG-TO-I          | DIGITAL CONVERTER                   |                                     |                 |                      |     |      |

|                      | ADC input voltage range             | At the input of the ADC (after PGA) | :               | 2 × V <sub>REF</sub> |     | V    |

| V <sub>IN</sub>      | Full-scale input voltage            | At the input of the PGA             | V <sub>AD</sub> | <sub>oc</sub> / Gain |     | V    |

| V <sub>REF</sub>     | Reference voltage                   |                                     |                 | 1.7                  |     | V    |

| R <sub>ON(mux)</sub> | Input multiplexer on-resistance     | $0 V \le V_{AAUX} \le AVDD$         |                 |                      | 6   | kΩ   |

|                      | AAUX input impedance                |                                     |                 | 4                    |     | MΩ   |

| f <sub>DR</sub>      | Output data rate                    |                                     | 8               |                      | 860 | SPS  |

|                      | Resolution                          |                                     | 16              |                      |     | Bits |

| E                    | Integral linearity error            | Best fit, DR = 8 SPS                |                 | 1                    |     | LSB  |

| <b>-</b>             | 0#                                  | Differential inputs                 |                 | ±1                   |     | LSB  |

| Eo                   | Offset error                        | Single-ended inputs                 |                 | ±3                   |     | LSB  |

| E <sub>G</sub>       | Gain error                          |                                     |                 | 0.05%                |     |      |

| V <sub>BAT_MON</sub> | Battery monitor output              |                                     | A               | VDD / 3              |     | V    |

| I <sub>BAT_MON</sub> | Battery monitor current consumption |                                     |                 | 1.5                  |     | μA   |

| IBAT_MON_ACC         | Battery monitor accuracy            |                                     |                 | ±2%                  |     |      |

| POWER CONS           | SUMPTION                            |                                     |                 |                      | ·   |      |

|                      |                                     | Power-down current                  |                 | 0.25                 |     | μA   |

|                      |                                     | Sleep-mode current                  |                 | 100                  |     | μA   |

|                      | Supply current                      | Weight-scale chain measurements     |                 | 540                  |     | μA   |

|                      |                                     | Body-composition measurements       |                 | 970                  |     | μA   |

|                      |                                     | Auxillary-channel measurements      |                 | 110                  |     | μA   |

## 6.8 Electrical Characteristics: Digital Input/Output

over operating free-air temperature range, AVDD – AVSS = 3 V (unless otherwise noted)

|                 | PARAMETER                 | MIN                    | TYP MA         | X UNIT      |     |

|-----------------|---------------------------|------------------------|----------------|-------------|-----|

| V <sub>IH</sub> | High-level input voltage  |                        | 0.75 ×<br>AVDD | AVD         | v c |

| V <sub>IL</sub> | Low-level input voltage   |                        | AVSS           | 0.25<br>AVD | V   |

| V <sub>OH</sub> | High-level output voltage | I <sub>OL</sub> = 1 mA | 0.8 ×<br>AVDD  |             | V   |

| V <sub>OL</sub> | Low-level output voltage  | I <sub>OL</sub> = 1 mA | GND            | 0.2<br>AVD  |     |

| I <sub>IN</sub> | Input current             |                        |                | ±30         | μA  |

SBAS586C -JUNE 2012-REVISED SEPTEMBER 2017

EXAS **NSTRUMENTS**

www.ti.com

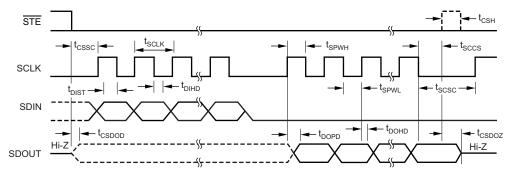

# 6.9 Timing Requirements: Serial Interface Timing

at  $T_A = 0^{\circ}C$  to +70°C and VDD = 2 V to 3.6 V (unless otherwise noted)

|                    |                                                                      | MIN | NOM | MAX | UNIT |

|--------------------|----------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>CSSC</sub>  | STE low to first SCLK setup time <sup>(1)</sup>                      | 100 |     |     | ns   |

| t <sub>SCLK</sub>  | SCLK period                                                          | 250 |     |     | ns   |

| t <sub>SPWH</sub>  | SCLK pulse duration high                                             | 100 |     |     | ns   |

| t <sub>SPWL</sub>  | SCLK pulse duration low                                              | 100 |     |     | ns   |

| t <sub>DIST</sub>  | Valid SDIN to SCLK falling edge setup time                           | 50  |     |     | ns   |

| t <sub>DIHD</sub>  | Valid SDIN to SCLK falling edge hold time                            | 50  |     |     | ns   |

| t <sub>DOPD</sub>  | SCLK rising edge to valid new SDOUT propagation delay <sup>(2)</sup> |     |     | 50  | ns   |

| t <sub>DOHD</sub>  | SCLK rising edge to DOUT invalid hold time                           | 0   |     |     | ns   |

| t <sub>CSDOD</sub> | STE low to SDOUT driven propagation delay                            | 100 |     |     | ns   |

| t <sub>CSDOZ</sub> | STE high to SDOUT Hi-Z propagation delay                             | 100 |     |     | ns   |

| t <sub>CSH</sub>   | STE high pulse                                                       | 200 |     |     | ns   |

| t <sub>SCCS</sub>  | Final SCLK falling edge to STE high                                  | 100 |     |     | ns   |

(1) (2)

$\overline{\text{STE}} \text{ can be tied low.} \\ \text{DOUT load} = 20 \text{ pF} \parallel 100 \text{ k}\Omega \text{ to DGND.} \\ \end{array}$

Figure 1. Serial Interface Timing

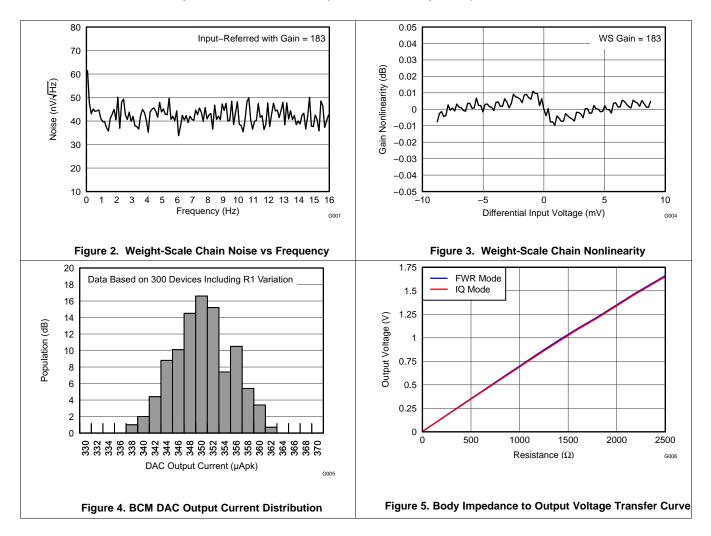

## 6.10 Typical Characteristics

all measurements at room temperature with AVDD = 3 V (unless otherwise specified)

## 7 Detailed Description

## 7.1 Overview

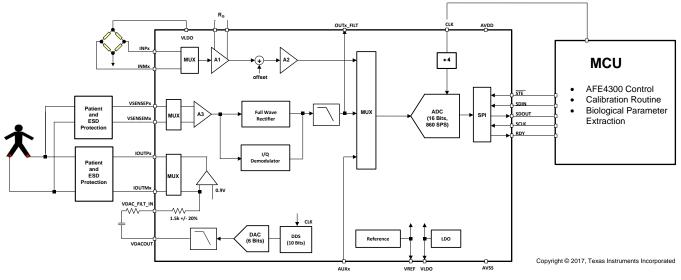

The AFE4300 is a low-cost, integrated front-end designed for weight scales incorporating body-composition measurements. The AFE4300 integrates all the components typically used in a weight scale. The device has two signal chains: one for weight scale measurements and the other for body composition measurements. Both signal chains share a 16-bit, delta-sigma converter that operates at a data rate of up to 860 SPS. This device also integrates a reference and a low-dropout regulator (LDO) that generates a 1.7-V supply that can be used as the excitation source for the load cells, thus simplifying ratiometric measurements. Both the signal chains use a single digital-to-analog converter (DAC). The DAC is used to generate the dc signal for load-cell offset cancellation in the weight-scale chain. The same DAC is also used to generate the sine-wave modulation signal for the body-composition signal chain. Therefore, only one of the two signal chains can be activated at a time (using the appropriate register bits).

Two unique features of the AFE4300 are that the device provides an option for connecting up to four separate load cells, and supports tetrapolar measurements with I/Q measurements.

## 7.2 Functional Block Diagram

## 7.3 Feature Description

This section describes the details of the AFE4300 internal functional elements. The analog blocks are reviewed first, followed by the digital interface. The theory behind the body-composition measurement using the full-wave rectification method and the I/Q demodulation method are also described. The analog front-end is divided in two signal chains: a weight-measurement chain and a body-composition measurement front-end chain; both use the same 16-bit ADC and 6-bit DAC.

Throughout this document:

- f<sub>CLK</sub> denotes the frequency of the signal at the CLK pin.

- t<sub>CLK</sub> denotes the period of the signal at the CLK pin.

- f<sub>DR</sub> denotes the output data rate of the ADC.

- t<sub>DR</sub> denotes the time period of the output data.

- f<sub>MOD</sub> denotes the frequency at which the modulator samples the input.

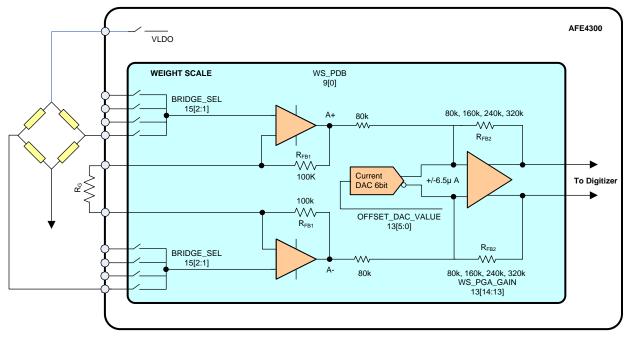

## 7.3.1 Weight-Scale Analog Front-End

Figure 6 shows a top-level view of the front-end section devoted to weight-scale measurement. The weight-scale front-end has two stages of gain, with an offset correction DAC in the second gain stage. The first-stage gain is set by the external resistor and the second-stage gain is set by progamming the internal registers. For access and programming information, see the *Register Maps* section.

Figure 6. Weight-Scale Front-End

Though not shown in the diagram, an antialiasing network is required in front of the INA to filter out electromagnetic interference (EMI) signals or any other anticipated interference signals. A simple RC network is sufficient, combined with the attenuation provided by the on-chip decimation filter.

An internal reference source provides a constant voltage of 1.7 V at the VLDO output to drive the external bridge. The output of the bridge is connected to an INA (first stage). The first-stage gain (A<sub>1</sub>) is set by the external resistor (R<sub>G</sub>) and the 100-k $\Omega$  (±5%) internal feedback resistors (R<sub>FB1</sub>) as shown in Equation 1:

$$A_1 = (1 + 2 \times 100 \text{ k/R}_G)$$

(1)

The second-stage gain (A<sub>2</sub>) is controlled by feedback resistors R<sub>FB2</sub>, which have four possible values: 80 k $\Omega$ , 160 k $\Omega$ , 240 k $\Omega$ , and 320 k $\Omega$ . Because the gain is R<sub>F</sub> / 80 k $\Omega$ , the gain setting can be 1, 2, 3, or 4. See the *Register Maps* section for details on setting the appropriate register bits.

TEXAS INSTRUMENTS

www.ti.com

(2)

## Feature Description (continued)

### 7.3.1.1 Input Common Mode Range

The usable input common mode range of the weight-scale front-end depends on various parameters, including the maximum differential input signal, supply voltage, and gain. The output of the first-stage amplifier must be within 250 mV of the power supply rails for linear operation. The allowed common-mode range is determined by Equation 2:

$$AVDD - 0.25 - \frac{GAIN \times V_{MAX\_DIFF}}{2} > CM > AVSS + 0.25 + \frac{GAIN \times V_{MAX\_DIFF}}{2}$$

Where:

- V<sub>MAX DIFF</sub> = maximum differential input signal at the input of the first gain stage,

- CM = Common-mode range.

For example, If AVDD = 2 V, the first stage gain = 183, and  $V_{MAX_DFF}$  = 7.5 mV (dc + signal), then: 1.06 V > CM > 0.936 V

## 7.3.1.2 Input Differential Dynamic Range

The max differential (INP – INN) signal depends on the analog supply, reference used in the system. This range is shown in Equation 3:

$$MAX(INP - INN) < \frac{VREF}{GAIN}; Full-Scale Range = 2 \times \frac{VREF}{GAIN}$$

(3)

The gain in Equation 3 is the product of the gains of the INA and the second-stage gain. The full-scale input from the bridge signal typically consists of a differential dc offset from the load cell plus the actual weight signal. Having a high gain in the first stage helps minimize the effect of the noise addition from the subsequent stages. However, make sure to choose a gain that does not saturate the first stage with the full-scale signal. Also, the common-mode of the signal must fall within the range, as per Equation 2.

### 7.3.1.3 Offset Correction DAC

One way to increase the dynamic range of the signal chain is by calibrating the inherent offset of the load cell during the initial calibration cycle. The offset correction is implemented in the second stage with a 6-bit differential DAC, where each output is a mirror of the other and can source or sink up to 6.5  $\mu$ A. The effect at the output of the second stage is an addition of up to ±6.5  $\mu$ A × 2 × R<sub>FB2</sub>. This effect is equivalent to a voltage at the input of the second stage (A+ / A–) of up to ±6.5  $\mu$ A × 2 × 80 kΩ = ±1 V, when R<sub>FB2</sub> = 80 kΩ. The first-stage saturation cannot be avoided using this DAC. Because the offset correction DAC is a 6-bit DAC, the offset compensation step is 2 V / 2<sup>6</sup> = 31.2 mV when referred to the input of the second stage.

### 7.3.1.3.1 Offset Correction Example

As an example, use a bridge powered from 1.7 V with 1.5 mV/V sensitivity and a potential offset between -4 mV and 4 mV. Worst case, the maximum signal is 4 mV of offset plus  $1.7 \times 1.5 \text{ mV/V} = 2.55 \text{ mV}$  of signal, for a total of 6.55 mV. The bridge common-mode voltage is ~0.85 V. The maximum excursion is 0.85 V - 0.25 V = 0.6 V (bottom rail) single-ended, on each output (A+ or A-). Therefore,  $\pm 1.2 \text{ V}$  differentially at the output of the first stage prevents saturation. This result means that the first stage can have up to a gain of 1.2 V / 6.55 mV = 183.

Using this same example, the swing at the output of the first stage corresponding only to the potential offset range is  $183 \times \pm 4 \text{ mV} = \pm 0.732 \text{ V}$ . This swing can be completely removed at the output of the second stage by the offset correction (because the offset correction DAC has a  $\pm 1$ -V range) except for a maximum error of 31.2 mV.

### Feature Description (continued)

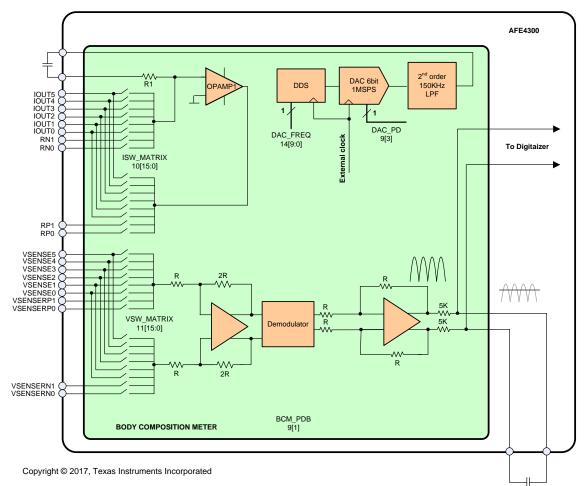

### 7.3.2 Body Composition Measurement Analog Front-End

Body composition is traditionally obtained by measuring the impedance across several points on the body and matching the result in a table linking both the impedance measured and the body composition. This table is created by each manufacturer and is usually based on age group, sex, weight, and other parameters.

The body impedance that we want to measure, Z(f), is a function of the excitation frequency, and can be represented by polar or cartesian notations:

$$Z(f) = |Z(f)| \cdot e^{j\theta(f)} = R(f) + jX(f)$$

where:

•

$$|Z| = sqrt(R^2 + X^2)$$

$$\theta = \operatorname{arctg}(X/R)$$

(4)

**AFE4300**

SBAS586C -JUNE 2012-REVISED SEPTEMBER 2017

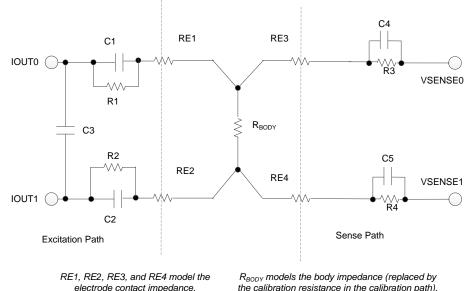

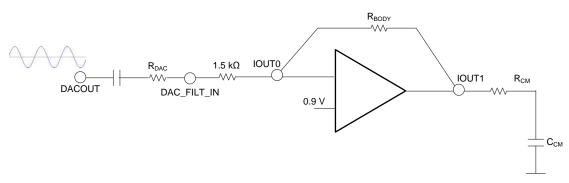

The AFE4300 provides two options for body impedance measurement: ac rectification and I/Q demodulation. Both options work by injecting a sinusoidal current into the body and measuring the voltage across the body. The portion of the circuit injecting the current into the body is the same for each of those options. The difference, however, lies in how the measured voltage across the impedance is processed to obtain the final result.

### 7.3.2.1 AC Rectification

Figure 7 shows the portion of the AFE4300 devoted to body composition measurement in the RMS detector mode.

Figure 7. BCM in AC Rectifier Mode

## Feature Description (continued)

The top portion of Figure 7 represents the current-injection circuit. A direct digital synthesizer (DDS) generates a sinusoidal digital pattern with a frequency obtained by dividing a 1-MHz clock with a 10-bit counter. The digital pattern drives a 6-bit, 1-MSPS DAC. The output of the DAC is filtered by a 150-kHz, second-order filter to remove the high-frequency images, followed by a series external capacitor to block the dc current and avoid any dc current injection into the body. The output of the filter (after the dc blocking capacitor) drives a resistor setting the amplitude of the current to be injected in the body, as shown in Equation 5:

$$I(t) = VDACOUT / R1 = A sin(w_0 t)$$

(5)

(6)

The nominal DACOUT voltage (VDACOUT) is 1.05 V<sub>PP</sub> (371.23  $\mu$ Vrms). The nominal value of R1 is 1.5 k $\Omega$ . So the nominal excitation current is 247.5  $\mu$ Arms. R1 can have a ±20% device-to-device variation, so the highest current is close to 300  $\mu$ Arms (850  $\mu$ A<sub>PP</sub>). The maximum voltage swing for the excitation electrodes (IOUT1-IOUT0) is 1 V<sub>PP</sub>. This swing limits the recommended total impedance in feedback to approximately 1175  $\Omega$ . To reduce the excitation current, place an external resistor, R<sub>DAC</sub>, (between DACOUT and DAC\_FILT\_IN) in series with R1. For example, with a 1.5-k $\Omega$  external resistor, the currents roughly reduce by 2X, thereby extending the range of the measured impedance.

Current flows into the body through an output analog multiplexer (mux) that allows the selection of up to six different contact points on the body. The same mux allows the connection of four external impedances for calibration. The current crosses the body impedance and a second mux selects the return path (contact) on the body, closing the loop to the output of the amplifier.

At the same time that the current is injected, a second set of multiplexers connects a differential amplifier across the same body impedance in order to measure the voltage drop created by the injected current, shown by Equation 6:

$$\mathbf{v}(t) = \mathbf{A} \left| \mathbf{Z} \right| \sin(\omega_0 t + \theta)$$

where Z and  $\theta$  are the module and phase of the impedance at  $\omega_0$ , respectively.

The output of the amplifier is routed to a pair of switches that implement the demodulation at the same frequency as the excitation current source in order to drive the control of those switches. This circuit performs a full-wave rectification of the differential amplifier output and a low-pass filter at the output, recovers the dc level, and finally routes the amplifier output to the same 16-bit digitizer used in the weight-scale chain.

$$DC = \frac{2}{T} \int_{T/2} A |Z| \sin\left(\omega_0 t + \theta\right) dt = \frac{2A|Z|}{\pi}$$

(7)

Ultimately, the dc output is proportional to the module of the impedance. The proportionality factor can be obtained through calibration with the four external impedances. Although, with one single frequency or measurement, only the module of the impedance can be obtained; two different frequencies could be used to obtain both the real and the imaginary parts.

## Feature Description (continued)

## 7.3.2.2 I/Q Demodulation

The AFE4300 includes a second circuit that with a single frequency measurement, obtains both the real and the imaginary portions, as shown in Figure 8. As explained previously, the portion of the circuit injecting the current into the body is the same for both configurations. Therefore, the circuit is the same in Figure 7 and Figure 8. The difference between them is that an I/Q demodulator is used in this second approach, as shown in Figure 8.

Figure 8. BCM in I/Q Demodulator Mode

As with the case of the RMS detector, a differential amplifier measures the voltage drop across the impedance, as shown in Equation 8:

$v(t) = A|Z|sin(\omega_0 t + \theta)$

where:

- Z = the module of the impedance at ω<sub>0</sub>

- $\theta$  = phase of the impedance at  $\omega_0$

(8)

The I/Q demodulator takes the v(t) signal and outputs two dc values. These two values are used to extract the impedance module and phase with a single frequency measurement. Figure 8 shows the block diagrm of the implementation. Using the I/Q demodulator helps reduce power consumption and still yields excellent performance. The local oscillator (LO) signals for the mixers are generated from the same clock driving the DDS/DAC and are of the same phase and frequency as the sinusoidal i(t) (see Equation 5). The LO signals directly control the switches on the in-phase (I) path, and after a delay of 90° degrees, control the switches on the quadrature (Q) path. This switching results in multiplying the v(t) signal by a square signal swinging from -1 to 1.

Copyright © 2012–2017, Texas Instruments Incorporated

## Feature Description (continued)

Breaking down the LO signal into Fourier terms results in Equation 9:

$$LO_{I}(t) = \frac{4}{\pi} (\sin(\omega_{0}t) + \frac{1}{3}\sin(3\omega_{0}t) + \frac{1}{5}\sin(5\omega_{0}t) + \dots)$$

(9)

Therefore, the output voltage of the mixer is as shown in Equation 10:

$$I(t) = A \left| Z \right| \frac{4}{\pi} (\sin(\omega_0 t + \theta) \sin(\omega_0 t) + \frac{1}{3} \sin(\omega_0 t + \theta) \sin(3\omega_0 t) + \frac{1}{5} \sin(\omega_0 t + \theta) \sin(5\omega_0 t) + \dots)$$

Where I(t) = in-phase output (not to be confused with i(t), the current injected in the impedance). (10)Applying fundamental trigonometry gives Equation 11:

sin a sin b =

$$-\frac{1}{2}\cos(a+b) + \frac{1}{2}\cos(a-b)$$

(11)

Each product of sinusoids can be broken up in an addition of two sinusoids. Equation 12 shows the first term:

$$\sin(\omega_0 t + \theta)\sin(\omega_0 t) = \frac{1}{2}\cos(\omega_0 t + \theta - \omega_0 t) - \frac{1}{2}\cos(\omega_0 t + \omega_0 t + \theta) = \frac{1}{2}\cos(\theta) - \frac{1}{2}\cos(2\omega_0 t + \theta)$$

(12)

Equation 13 shows the 2nd product:

$$\sin(\omega_0 t + \theta)\sin(3\omega_0 t) = \frac{1}{2}\cos(\omega_0 t + \theta - 3\omega_0 t) - \frac{1}{2}\cos(3\omega_0 t + \omega_0 t + \theta) = \frac{1}{2}\cos(-2\omega_0 t + \theta) - \frac{1}{2}\cos(4\omega_0 t + \theta)$$

(13)

And so on. Performing the same analysis on the Q side, the output voltage of the mixer is shown in Equation 14:

$$Q(t) = A \left| Z \right| \frac{4}{\pi} (\sin(\omega_0 t + \theta) \cos(\omega_0 t) + \frac{1}{3} \sin(\omega_0 t + \theta) \cos(3\omega_0 t) + \frac{1}{5} \sin(\omega_0 t + \theta) \cos(5\omega_0 t) + \dots)$$

(14)

Agiain, applying fundamental trigonometry gives Equation 15:

sin a cos b =

$$\frac{1}{2}$$

sin(a+b) +  $\frac{1}{2}$ sin(a-b) (15)

Each of the products can be broken up into sums. Starting with the first product, as shown in Equation 16:

$$\sin(\omega_0 t + \theta)\cos(\omega_0 t) = \frac{1}{2}\sin(2\omega_0 t + \theta) + \frac{1}{2}\sin(\theta)$$

(16)

And so on. Note that on I(t) as well as on Q(t), all the terms beyond the cutoff frequency of the low-pass filter at the output of the mixers (setup by the two 1-k $\Omega$  resistors and an external capacitor) are removed, leaving only the dc terms, giving Equation 17 for I<sub>DC</sub> and Equation 18 for Q<sub>DC</sub>:

$$I_{DC} = \frac{2A|Z|}{\pi} \cos(\theta) = K|Z|\cos(\theta)$$

(17)

$$Q_{DC} = \frac{2A|Z|}{\pi} \sin(\theta) = K|Z|\sin(\theta)$$

(18)

In reality, the LO amplitude is not known (likely, not ±1) and affects the value of K in Equation 17 and Equation 18. Solving these two equations gives Equation 19:

$$\theta = \arctan \frac{Q_{DC}}{I_{DC}}$$

$$Z = \frac{1}{K} \sqrt{I_{DC}^2 + Q_{DC}^2}$$

(19)

In order to account for all the nonidealities in the system, the AFE4300 also offers four extra terminals on the driving side (two to drive, and two for the currents to return) and four extra terminals on the receive/differentialamplifier side. As with RMS mode, these spare terminals allow for connection of up to four external calibration impedances, and they also compute K.

## Feature Description (continued)

## 7.3.3 Digitizer

The digitizer block includes an analog mux and a 16-bit sigma-delta ADC.

### 7.3.3.1 Multiplexer

There are two levels of analog mux. The first level selects from among the outputs of the weight scale, the body composition function, two auxiliary inputs, and the battery monitor. A second mux is used to obtain the measurement of the outputs coming from the first mux, either differentially or with respect to ground (single-ended). Note that when measuring single-ended inputs, the negative range of the output codes are not used. For battery or AVDD monitoring, an internal 1/3 resistor divider is included that enables the measurement using only one reference setting for any battery voltage, thus simplifying the monitoring routine.

## 7.3.3.2 Analog-to-Digital Converter

The 16-bit, delta-sigma, ADC operates at a modulator frequency of 250 kHz with an  $f_{CLK}$  of 1 MHz. The full-scale voltage of the ADC is set by the voltage at the reference ( $V_{REF}$ ). The reference can be either the LDO output (1.7 V) for the weight-scale front-end or the internally-generated reference signal (1.7 V) for the BCM front-end.

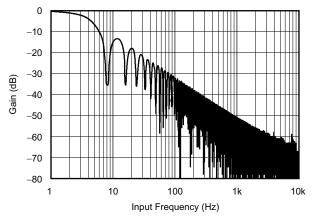

The decimation filter at the output of the modulator is a single-order sinc filter. The decimation rate can be programmed to provide data rates from 8 SPS to 860 SPS with an  $f_{CLK}$  of 1 MHz. Refer to the ADC\_CONTROL\_REGISTER1 register in the *Register Maps* section for details on programming the data rates. Figure 9 shows the frequency response of the digital filter for a data rate of 8 SPS. Note that the modulator has pass band around integer multiples of the modulator sampling frequency of 250 kSPS. Set the corner frequency of the antialiasing network before the INA so that there is adequate attenuation at the first multiple of the modulator frequency.

Figure 9. Frequency Response

The output format of the ADC is twos complement binary. Table 1 describes the output code versus the input signal, where full-scale (FS) is equal to the  $V_{REF}$  value.

| IDEAL OUTPUT CODE |

|-------------------|

| 7FFFh             |

| 0001h             |

| 0                 |

| FFFFh             |

| 8000h             |

|                   |

### AFE4300

SBAS586C -JUNE 2012-REVISED SEPTEMBER 2017

www.ti.com

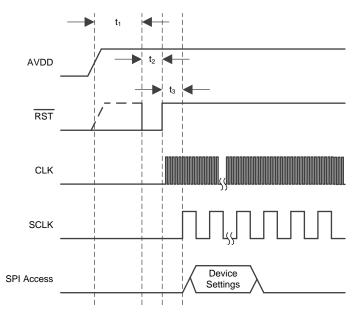

### 7.3.4 Reset and Power-Up

After power up, the device needs to be reset to get all the internal registers to their default state. Resetting the device is done by applying a zero pulse in the RST line for more than 20 ns after the power is stable for 5 ms. After 30 ns, the first access can be initiated (first falling edge of STE). As part of the reset process, the AFE4300 sets all of the register bits to the respective default settings. Some of the register bits must be written after reset and power up for proper operation. Refer to the *Register Maps* section for more details. By default, the AFE4300 enters into a power-down state at start-up. The device interface and digital are active, but no conversion occurs until the ADC\_PD bit is written to. The initial power-down state of the AFE4300 is intended to relieve systems with tight power-supply requirements from encountering a surge during power-up.

## 7.3.5 Duty Cycling for Low Power

For many applications, improved performance at low data rates may not be required. For these applications, the AFE4300 supports duty cycling that can yield significant power savings by periodically requesting high data-rate readings at an effectively lower data rate. For example, an AFE4300 in power-down mode with a data rate set to 860 SPS could be operated by a microcontroller that instructs a single-shot conversion every 125 ms (8 SPS). Because a conversion at 860 SPS only requires approximately 1.2 ms, the AFE4300 automatically enters power-down mode for the remaining 123.8 ms. In this configuration, the digitizer consumes about 1/100th the power of the digitizer when operated in Continuous-Conversion mode. The rate of duty cycling is completely arbitrary and is defined by the master controller.

## 7.4 Device Functional Modes

## 7.4.1 Operating Modes

The ADC operates in one of two conversion modes: Continuous-Conversion or Single-Shot conversion. The conversion mode is set using the ADC\_CONV\_MODE bit. In Continuous-Conversion mode, the ADC continuously performs conversions when the ADC\_PD bit is set to 0. When a conversion completes, the ADC places the result in a register, issues an interrupt on the RDY pin, and immediately begins another conversion. In this mode, if ADC\_PD is set to 1, then the ADC goes into a power-down state.

To get a Single-Shot conversion, the ADC\_PD bit is to be first set to 1. When the ADC\_CONV\_MODE is subsequently set to 1, then the Single-Shot conversion is enabled. When enabled, the ADC does a single conversion and gives an interrupt on the RDY pin. To do one more Single-Shot conversion, the ADC\_CONV\_MODE bit must be set to 0 and then 1 again (with the ADC\_PD bit at 1).

## 7.5 Programming

**AFE4300**

SBAS586C - JUNE 2012 - REVISED SEPTEMBER 2017

The SPI<sup>™</sup>-compatible serial interface consists of either four signals (STE, SCLK, SDIN, and SDOUT) or three signals (in which case, STE can be tied low). The interface is used to read conversion data, read from and write to registers, and control AFE4300 operation. The data packet (between falling and rising edge of STE) is 24 bits long and is serially shifted into SDIN with the MSB first. The first eight bits (MSB) represent the address of the register being accessed and last 16 bits (LSB) represent the data to be stored or read from that address. For the eight bits address, the lower five bits [20:16] are the real address bits. Bit 21 is the read and write bit.

- '0' in bit 21 defines a write operation of the 16 data bits [15:0] into the register defined by the address bits [20:16].

- '1' in bit 21 triggers a read operation of the register defined by the address bits [20:16]. The data are output

into SDOUT with every rising edge of SCLK, starting at the ninth rising edge. At the same time, data in SDIN

are shifted inside the 16 data bits of that given register. Note that every time a register is read, the register

must be rewritten except when reading the data output register.

## 7.5.1.1 SPI Enable (STE)

The STE pin selects the AFE4300 for SPI communication. This feature is useful when multiple devices share the serial bus. STE must remain low for the duration of the serial communication. When STE is taken high, the serial interface is reset, and SCLK is ignored.

## 7.5.1.2 Serial Clock (SCLK)

The SCLK pin features a Schmitt-triggered input and is used to clock data on the DIN and  $\overline{RDY}$  pins into and out of the AFE4300. Even though the input has hysteresis, SCLK is recommended to be kept as clean as possible to prevent glitches from accidentally shifting the data. When the serial interface is idle, hold SCLK low.

### 7.5.1.3 Data Input (SDIN)

The data input pin (SDIN) is used along with SCLK to send data to the AFE4300 (opcode commands and register data). The device latches data on SDIN on the falling edge of SCLK. The AFE4300 never drives the SDIN pin. Note that every time a register is read, the register must be rewritten, except when reading the data output register.

## 7.5.1.4 Data Output (SDOUT)

The data output and data ready pin ( $\overline{\text{RDY}}$ ) are used with SCLK to read conversion and register data from the AFE4300. In Read Data Continuous mode, RDY goes low when conversion data are ready, and goes high 8  $\mu$ s before the data ready signal. Data on RDY are shifted out on the rising edge of SCLK. If the AFE4300 does not share the serial bus with another device, STE may be tied low. Note that every time a register is read, the register must be rewritten, except when reading the data output register.

## **Programming (continued)**

## 7.5.1.5 Data Ready (RDY)

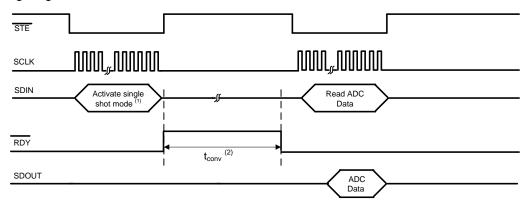

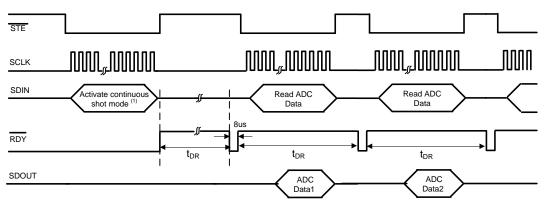

$\overline{\text{RDY}}$  acts as a conversion ready pin in both Continous-Conversion mode and <u>Single-Shot</u> mode. When in Continuous-Conversion mode, the AFE4300 provides a brief (~8 µs) pulse on the RDY pin at the end of each conversion. In Single-Shot mode, the RDY pin asserts low at the end of a conversion. Figure 10 and Figure 11 show the timing diagram for these two modes.

Note 1 : Write ADC\_CONTROL\_REGISTER[7] = 1, ADC\_CONTROL\_REGISTER1[15] = 1, Note 2 : t<sub>CONV</sub> = Time to internally set ADC\_CONTROL\_REGISTER[15] to logic '0', ADC power up, single conversion, ADC power down, ADC\_CONTROL\_REGISTER1[15] internally set to logic '1'

Figure 10. Timing for Single-Shot Mode

Note 1 : Write ADC\_CONTROL\_REGISTER[7] = 0

## Figure 11. Timing for Continuous Mode

## 7.6 Register Maps

## 7.6.1 Register Map

Table 2 describes the registers of the AFE4300.

| REGISTER NAME           | CONTROL                  | ADDRESS     | DESCRIPTION                                         | DEFAULT |

|-------------------------|--------------------------|-------------|-----------------------------------------------------|---------|

| DEVICE CONTROLS         |                          |             |                                                     |         |

|                         | (See Description)        | 0x09[14:13] | Write '11' after power up and/or reset              | 00b     |

|                         | DAC_PD                   | 0x09[3]     | Enable DAC for WS, BC measurements                  | 0b      |

|                         | PDB                      | 0x09[2]     | Chip power down                                     | 0b      |

| DEVICE_CONTROL1         | BCM_PDB                  | 0x09[1]     | Body composition measurement front-end power down   | 0b      |

|                         | WS_PDB                   | 0x09[0]     | Weight-scale front-end power down                   | 0b      |

|                         | BAT_MON_EN1              | 0x0F[7]     | Enables battery monitoring along with bit[0]        | 0b      |

| DEVICE_CONTROL2         | BAT_MON_EN2              | 0x0F[0]     | Enables battery monitoring along with bit[7]        | 0b      |

| ADC CONTROLS            |                          |             |                                                     |         |

| ADC_DATA_RESULT         | (See Description)        | 0x00[15:0]  | ADC data result, read only register                 |         |

|                         | ADC_CONV_MODE            | 0x01[15]    | Continuous-Conversion or Single-Shot mode           | 0b      |

|                         | ADC_MEAS_MODE            | 0x01[13:11] | Single-Ended or Differential mode                   | 000b    |

| ADC_CONTROL_REGISTER1   | ADC_PD                   | 0x01[7]     | ADC power down                                      | 1b      |

|                         | ADC_DATA_RATE            | 0x01[6:4]   | ADC data-rate control bits                          | 100b    |

|                         | ADC_REF_SEL              | 0x10[6:5]   | Reference selection bits                            | 00b     |

| ADC_CONTROL_REGISTER2   | PERIPHERAL_SEL           | 0x10[4:0]   | Peripheral selection bits                           | 00000b  |

| WEIGHT-SCALE MODES      |                          |             |                                                     |         |

| DEVICE_CONTROL2         | BRIDGE_SEL               | 0x0F[2:1]   | Selects one of the four bridge inputs               | 00b     |

|                         | WS_PGA_GAIN              | 0x0D[14:13] | PGA gain of weight-scale front-end                  | 00b     |

| WEIGHT_SCALE_CONTROL    | OFFSET_DAC_VALUE         | 0x0D[5:0]   | Offset DAC setting for weight-scale front-end       | 000000b |

| BCM CONTROLS            | •                        |             | -                                                   |         |

|                         | ISW_MUXP                 | 0x0A[15:8]  | Control for switches IOUTP and RP                   | 0x00    |

| ISW_MUX                 | ISW_MUXM                 | 0x0A[7:0]   | Control for switches IOUTN and RN                   | 0x00    |

|                         | VSENSE_MUXP              | 0x0B[15:8]  | Control for switches VSENSEP and VSENSEP_R          | 0x00    |

| VSENSE_MUX              | VSENSE_MUXM              | 0x0B[7:0]   | Control for switches VSENSEN and VSENSN_R           | 0x00    |

| BCM_DAC_FREQ            | DAC_FREQ                 | 0x0E[9:0]   | Sets the frequency of BCM excitation current source | 0x00    |

| IQ_MODE_ENABLE          | IQ_MODE_ENABLE           | 0x0C[11]    | Enable IQ demodulator                               | 0b      |

| DEVICE_CONTROL2         | IQ_DEMOD_CLK_DIV_<br>FAC | 0x0F[13:11] | IQ Demodulator clock frequency                      | 000b    |

| MISCELLANEOUS REGISTERS | 6                        |             |                                                     |         |

| MISC_REGISTER1          | (See Description)        | 0x02[15:0]  | Write 0x0000 after power up and/or reset            | 0x8000  |

| MISC_REGISTER2          | (See Description)        | 0x03[15:0]  | Write 0xFFFF after power up and/or reset            | 0x7FFF  |

| MISC_REGISTER3          | (See Description)        | 0x1A[15:0]  | Write 0x0030 after power up and/or reset            | 0x0000  |

### Table 2. Register Map

AFE4300

SBAS586C-JUNE 2012-REVISED SEPTEMBER 2017

## 7.6.1.1 ADC\_DATA\_RESULT (Address 0x00, Default 0x0000)

This register stores the most recent conversion data in twos complement format with the MSB in bit 15 and the LSB in bit 0.

## 7.6.1.2 ADC\_CONTROL\_REGISTER1 (Address 0x01, Default 0x01C3)

This register is used in conjunction with ADC\_PD (bit 7). Refer to the description of the ADC\_PD bit for more details.

| 15                | 14 | 13   | 12     | 11   | 10 | 9 | 8 | 7          | 6    | 5       | 4    | 3 | 2 | 1 | 0 |

|-------------------|----|------|--------|------|----|---|---|------------|------|---------|------|---|---|---|---|

| ADC_CON<br>V_MODE | 1  | ADC_ | MEAS_M | NODE | 0  | 0 | 1 | ADC_<br>PD | ADC_ | _DATA _ | RATE | 0 | 0 | 0 | 0 |

#### Bit 15

#### ADC\_CONV\_MODE: ADC conversion mode/ADC single-shot conversion start.

This bit determines the operational status of the device. This bit can only be written when in the ADC power-down mode. When read, this bit gives the status report of the conversion.

For a write status:

0 : No effect (default)

1 : Single-shot conversion mode

For a read status:

- 0 : Device currently performing a conversion

- 1 : Device not currently performing a conversion

#### Bit 14 Always write '1'.

#### Bits[13:11] ADC\_MEAS\_MODE: ADC measurement mode selection.

These bits set the ADC measurements to be either single-ended or differential.

| ADC_MEAS_MODE | ADC AINP, AINM                  |

|---------------|---------------------------------|

| 000 (default) | A1, A2 = differential (default) |

| 001           | A1, AVSS = single-ended         |

| 010           | A2, AVSS = single-ended         |

#### Bits[10:8] Always write '001'

#### Bit 7 ADC\_PD: ADC Powerdown