32-BIT ARM926EJ-S BASED MCU

# NUC950ADN 32-bit ARM926EJ-S Based Microcontroller Product Data Sheet

The information described in this document is the exclusive intellectual property of Nuvoton Technology Corporation and shall not be reproduced without permission from Nuvoton.

Nuvoton is providing this document only for reference purposes of ARM926-based system design. Nuvoton assumes no responsibility for errors or omissions.

All data and specifications are subject to change without notice.

For additional information or questions, please contact: Nuvoton Technology Corporation.

1

## 32-BIT ARM926EJ-S BASED MCU

## Table of Contents

| 1. | GEN  | ERAL D  | ESCRIPTION                                 |                                         |

|----|------|---------|--------------------------------------------|-----------------------------------------|

| 2. | FEAT | FURES . |                                            | 7                                       |

| 3. | PIN  | DIAGR   | АМ                                         |                                         |

| 4. | PIN  | ASSIG   |                                            |                                         |

| 5. | PIN  | DESCR   | IPTION                                     |                                         |

|    | 5.1  | Pin De  | escription for Interface                   |                                         |

|    | 5.2  | GPIO    | Share Pin Description                      |                                         |

| 6. | FUN  |         |                                            |                                         |

| 7. |      |         |                                            |                                         |

|    | 7.1  |         |                                            |                                         |

|    | 7.2  |         |                                            |                                         |

|    | /.2  | 7.2.1   | 5                                          |                                         |

|    |      | 7.2.2   |                                            |                                         |

|    |      | 7.2.2   | , , ,                                      |                                         |

|    |      | 7.2.4   |                                            |                                         |

|    |      | 7.2.5   |                                            |                                         |

|    |      | 7.2.6   | _                                          |                                         |

|    |      | 7.2.7   | , 5                                        |                                         |

|    | 7.3  | Clock   |                                            |                                         |

|    |      | 7.3.1   |                                            |                                         |

|    |      | 7.3.2   | Clock Control Registers Map                | 54                                      |

|    | 7.4  | Exterr  | nal Bus Interface                          |                                         |

|    |      | 7.4.1   | Overview                                   | 74                                      |

|    |      | 7.4.2   | Functional Description                     | 75                                      |

|    |      | 7.4.3   | EBI Register Mapping                       |                                         |

|    |      | 7.4.4   | EBI Register Details                       |                                         |

|    | 7.5  | Etherr  | net MAC Controller                         |                                         |

|    |      | 7.5.1   | EMC Descriptors                            | 97                                      |

|    |      | 7.5.2   | EMC Register Mapping                       |                                         |

|    |      | 7.5.3   | EMC Register Details                       |                                         |

|    |      | 7.5.4   | Operation Notes                            |                                         |

|    | 7.6  | GDMA    | Controller                                 |                                         |

|    |      | 7.6.1   | Overview & Features                        |                                         |

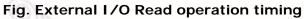

|    |      | 7.6.2   | GDMA Non-Descriptor Functional Description | tion165                                 |

|    |      |         | 2                                          | Publication Release Date: Jun. 18, 2010 |

|      | 32-BIT ARM926EJ-S BASED                         | MCU |

|------|-------------------------------------------------|-----|

|      | 7.6.3 GDMA Descriptor Functional Description    | 165 |

|      | 7.6.4 GDMA Register Map                         | 170 |

| 7.7  | USB Host Controller (USBH)                      | 189 |

|      | 7.7.1 Register Mapping                          | 190 |

|      | 7.7.2 Register Details                          | 192 |

| 7.8  | USB 2.0 Device Controller                       | 254 |

|      | 7.8.1 USB Device Register Group Summary         | 254 |

|      | 7.8.2 USB Device Control Registers Map          | 254 |

|      | 7.8.3 USB Device Control Registers              | 258 |

|      | 7.8.4 DMA Controller (DMAC)                     | 306 |

|      | 7.8.5 DMA Controller Registers Map              | 306 |

|      | 7.8.6 DMAC Registers                            | 307 |

| 7.9  | Flash Memory Interface Controller (FMI)         | 313 |

|      | 7.9.1 FMI Controller Registers Map              | 313 |

|      | 7.9.2 Register Details                          | 315 |

| 7.10 | LCD Display Interface Controller (LCM)          |     |

|      | 7.10.1 LCD Controller Function Description      | 378 |

|      | 7.10.2 LCD Controller Register Map              | 379 |

|      | 7.10.3 LCD Controller Register                  | 381 |

| 7.11 | Audio Controller                                | 438 |

|      | 7.11.1 IIS Interface                            | 438 |

|      | 7.11.2 AC97 Interface                           | 439 |

|      | 7.11.3 Audio Controller Register Map            | 440 |

| 7.12 | 2-D Graphic Engine                              | 468 |

|      | 7.12.1 2-D Graphic Engine Control Registers Map | 469 |

|      | 7.12.2 2-D Graphic Engine Control Registers     | 470 |

| 7.13 | UART Controller                                 | 499 |

|      | 7.13.1 UART Feature Description                 | 500 |

|      | 7.13.2 UART Control Registers Map               | 501 |

| 7.14 | TIMER Controller                                | 517 |

|      | 7.14.1 General Timer Controller                 | 517 |

|      | 7.14.2 Watchdog Timer                           | 518 |

|      | 7.14.3 Timer Control Registers Map              | 519 |

| 7.15 | Advanced Interrupt Controller                   | 529 |

|      | 7.15.1 AIC Registers Map                        | 531 |

| 7.16 | General-Purpose Input/Output (GPIO)             |     |

|      | 7.16.1 Overview                                 |     |

|      | 7.16.2 GPIO Multiplexed Functions Table         |     |

|      | 3 Publication Poloaso Dato: Jun                 |     |

8.

9.

|     |      | 7.16.3 | GPIO Control Registers Map                       | 552                       |

|-----|------|--------|--------------------------------------------------|---------------------------|

|     | 7.17 | I2C Sy | ynchronous Serial Interface Controller           | 571                       |

|     |      | 7.17.1 | I2C Serial Interface Control Registers Map       | 572                       |

|     | 7.18 | Univer | rsal Serial Interface Controller (USI)           |                           |

|     |      | 7.18.1 | USI Control Registers Map                        |                           |

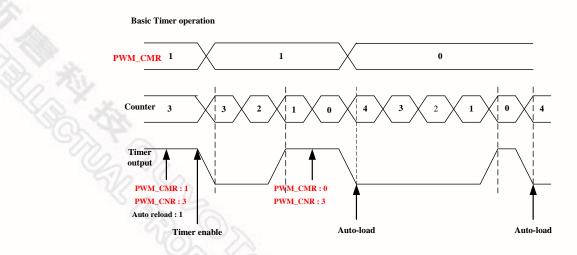

|     |      | 7.18.2 | Basic Timer Operation                            |                           |

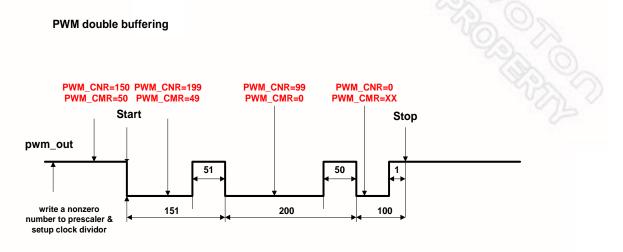

|     |      | 7.18.3 | PWM Double Buffering and Reload Automatically    | 590                       |

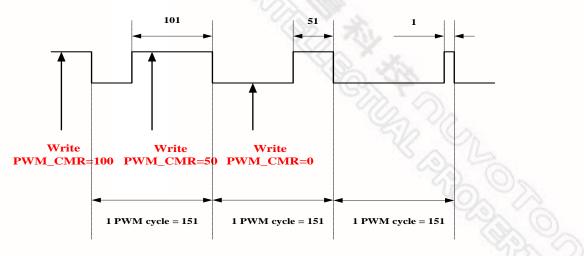

|     |      | 7.18.4 | Modulate Duty Ratio                              |                           |

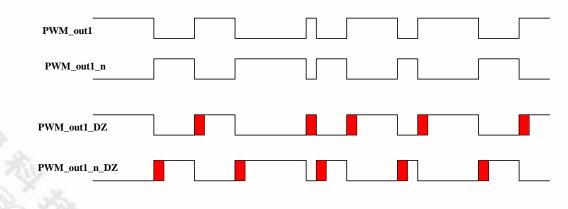

|     |      | 7.18.5 | Dead Zone Generator                              | 592                       |

|     |      | 7.18.6 | PWM Register Map                                 | 592                       |

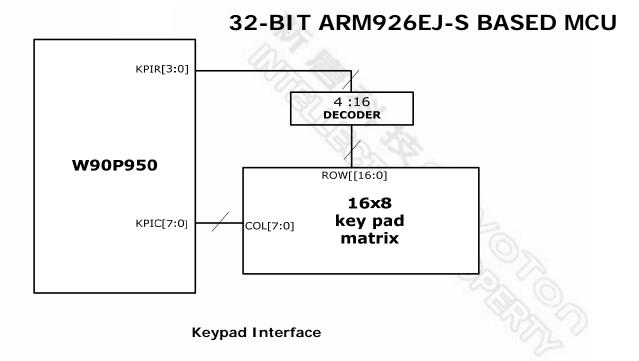

|     | 7.19 | Кеура  | Id Interface (KPI)                               | 604                       |

|     |      | 7.19.1 |                                                  |                           |

| 8.  | ELEC | TRICAL | _ SPECIFICATIONS                                 | 612                       |

|     | 8.1  | Absolu | Ite Maximum Ratings                              | 612                       |

|     | 8.2  |        | ecifications                                     |                           |

|     | 0.2  | 8.2.1  | Digital DC Characteristics                       |                           |

|     |      | 8.2.2  | USB Low-/Full-Speed DC Electrical Specifications |                           |

|     |      | -      | USB High-Speed DC Electrical Specifications      |                           |

|     | 8.3  |        | ecifications                                     |                           |

|     | 0.5  | 8.3.1  | RESET AC Characteristics                         |                           |

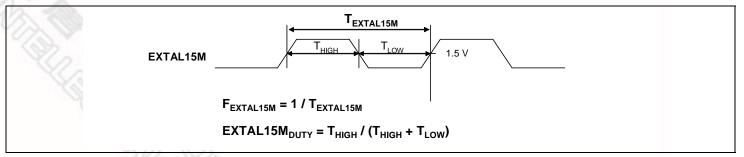

|     |      | 8.3.2  | Clock Input Characteristics                      |                           |

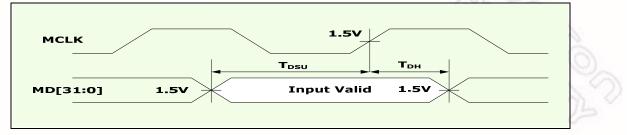

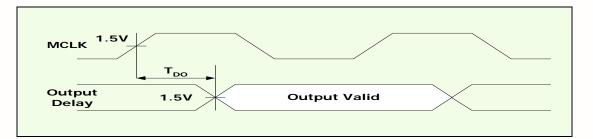

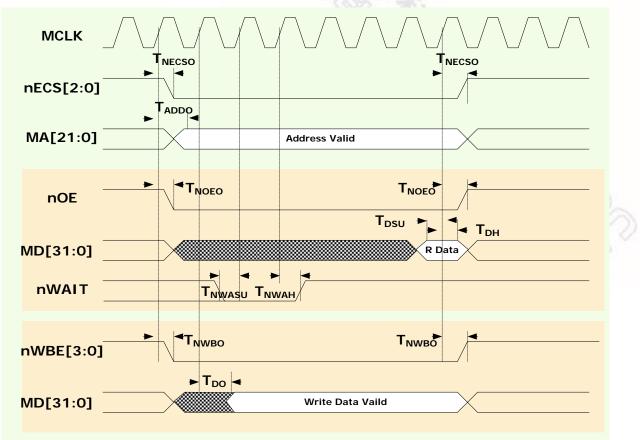

|     |      | 8.3.3  | EBI/SDRAM Interface AC Characteristics           |                           |

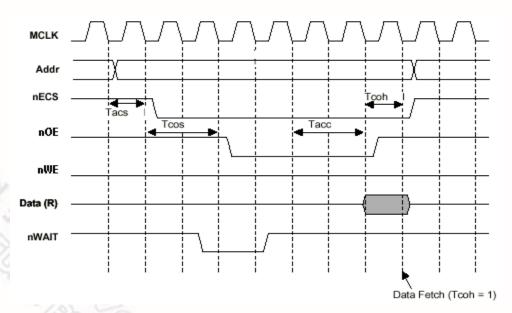

|     |      | 8.3.4  | EBI/ (ROM/SRAM/External I/O) AC Characteristics  |                           |

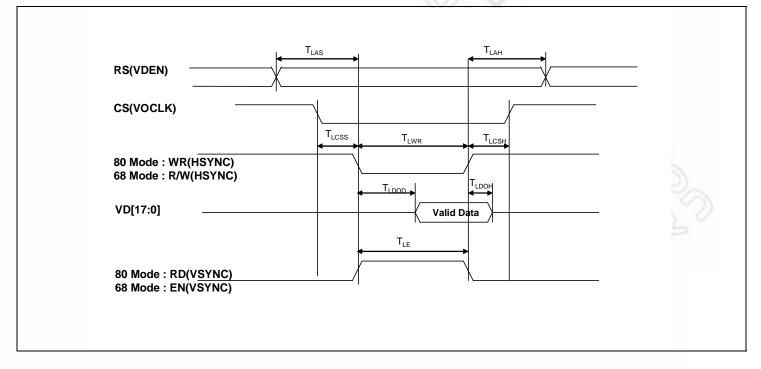

|     |      | 8.3.5  | LCD Interface: MPU Type AC Characteristics       |                           |

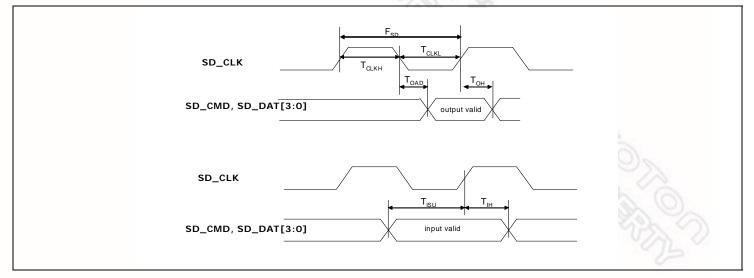

|     |      | 8.3.6  | SD Host Interface AC Characteristics             | 618                       |

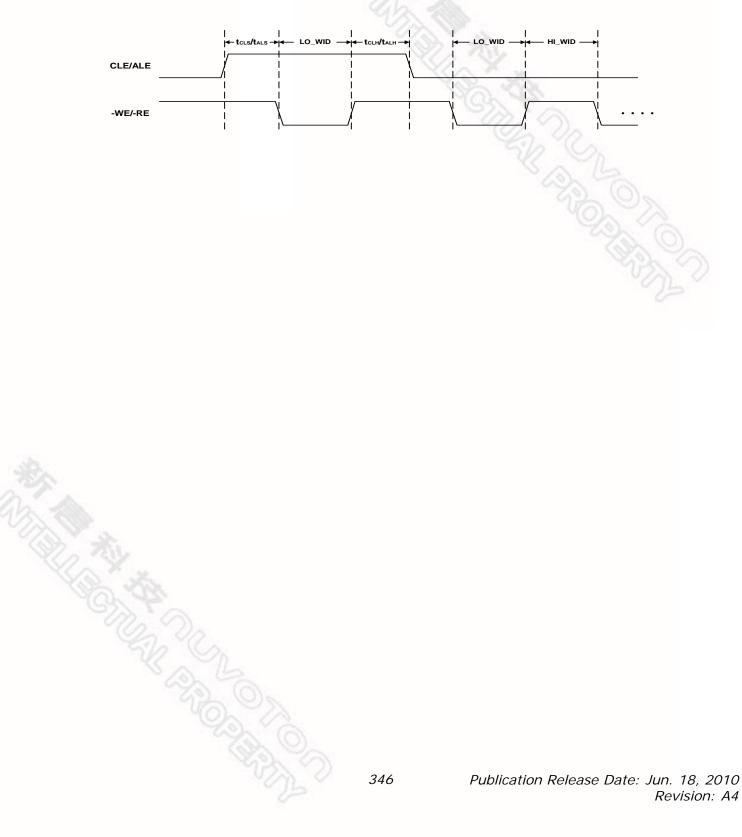

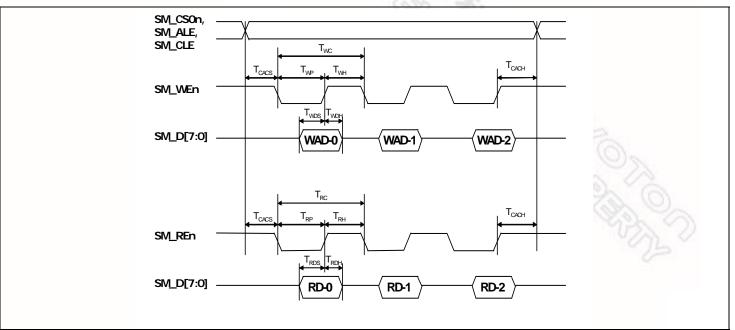

|     |      | 8.3.7  | NAND Flash Memory Interface AC Characteristics   | 619                       |

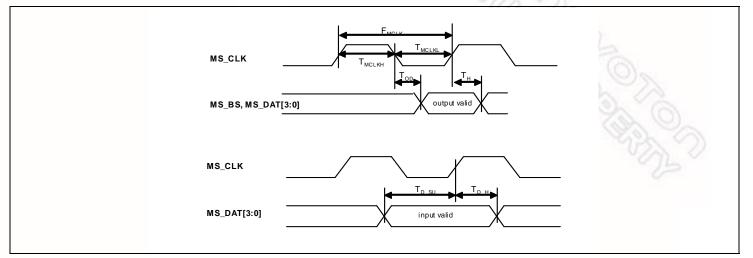

|     |      | 8.3.8  | Memory Stick Interface AC Characteristics        | 620                       |

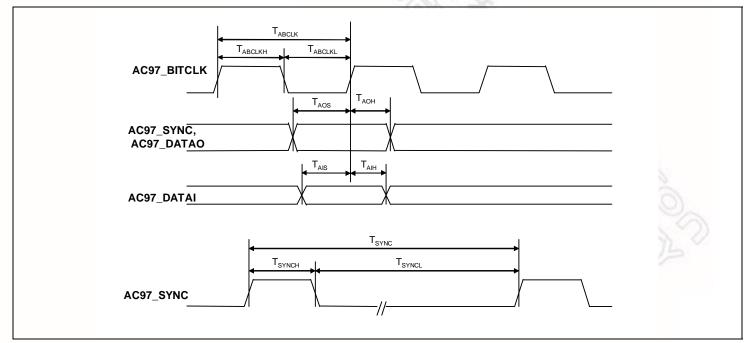

|     |      | 8.3.9  | Audio AC-Link Interface AC Characteristics       | 621                       |

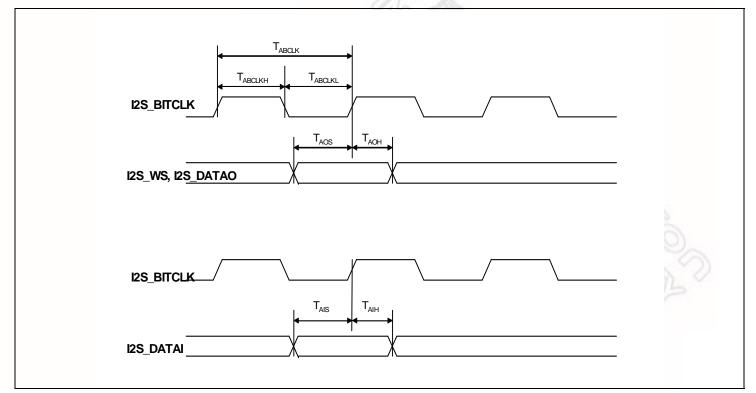

|     |      | 8.3.10 | Audio I2S Interface AC Characteristics           | 622                       |

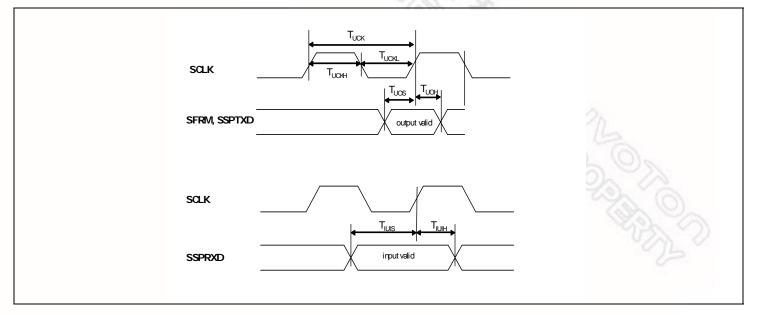

|     |      | 8.3.11 | USI (SPI/MW) Interface AC Characteristics        | 623                       |

|     |      | 8.3.12 | USB Transceiver AC Characteristics               | 624                       |

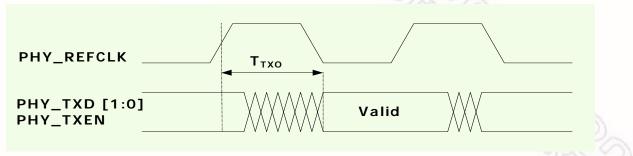

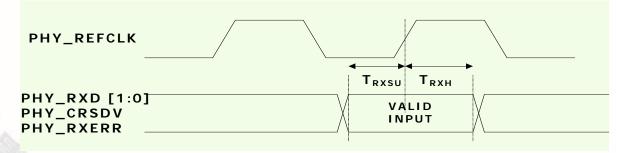

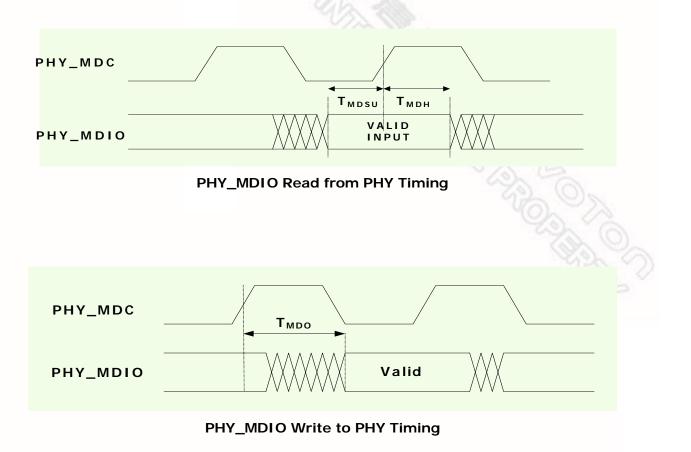

|     |      | 8.3.13 | EMC RMII AC Characteristics                      | 625                       |

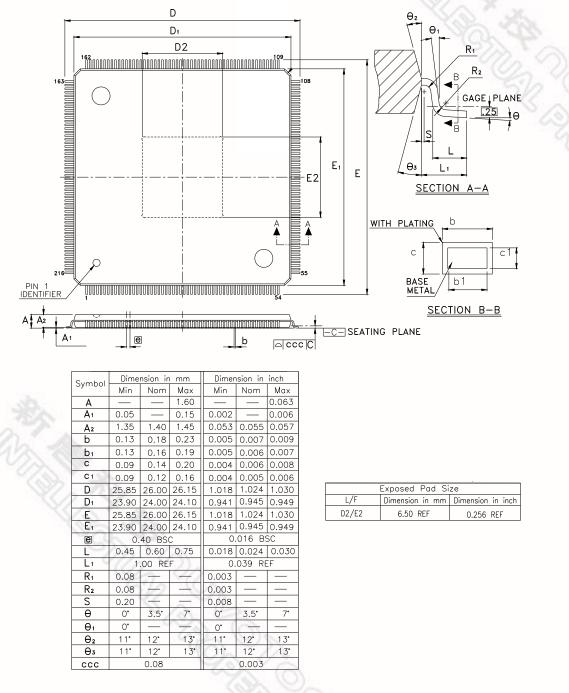

| 9.  | PACK | AGE SF | PECIFICATIONS                                    | 627                       |

| 10. | REVI | SION H | II STORY                                         | 628                       |

|     |      |        |                                                  |                           |

|     |      |        |                                                  |                           |

|     |      |        |                                                  |                           |

|     |      |        |                                                  |                           |

|     |      |        | 4 Publication Release Date: Jun<br>Re            | . 18, 2010<br>evision: A4 |

### 32-BIT ARM926EJ-S BASED MCU

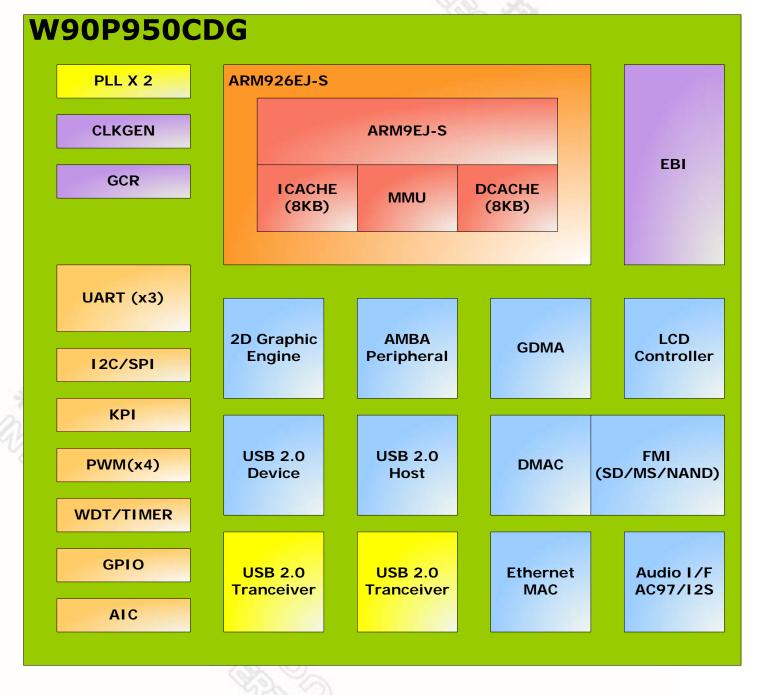

### 1. GENERAL DESCRIPTION

This chip is built around an outstanding CPU core: the 16/32 ARM926EJ-S RISC processor designed by Advanced RISC Machines, Ltd. The ARM926EJ-S core, offers 8K-byte I-cache and 8K-byte D-cache with MMU, is a low power, general-purpose integrated circuits. One 10/100 Mb MAC of Ethernet controller is builtin to reduce total system cost. A TFT type LCD controller and 2D graphics engine with various integrated on chip functions, this micro-controller is suitable for a high end, high performance and low cost related products as well as general purpose applications.

The following integrated on-chip functions are described in detail in this document.

|                    | Main Function                                      |

|--------------------|----------------------------------------------------|

| CPU                | ARM926EJ-S                                         |

| Platform           | Programmable PLL System Clock Synthesizer          |

|                    | AMBA Peripherals                                   |

|                    | Timer, Watchdog Timer                              |

|                    | Advanced Interrupt Controller                      |

|                    | General DMA Controller                             |

|                    | External Bus Interface Controller                  |

| Networking         | Ethernet MAC Controller                            |

| Display Interface  | LCD Controller                                     |

| Graphics           | 2D Graphic Engine                                  |

| Audio Interface    | 2-Channel I2S Controller                           |

| b.                 | 2-Channel AC97 Controller                          |

| USB Interface      | USB 1.1/2.0 High/Full/Low Speed Host<br>Controller |

| Solar Contract     | USB 2.0 High/Full Speed Device Controller          |

| Storage Interface  | NAND Flash Controller with ECC1/ECC4               |

| OL Dr.             | SD/SDIO/MMC Controller                             |

| Sh On              | Memory Stick (MS) Controller                       |

| Peripheral & Misc. | • GPIO                                             |

| 12 C               | • 4-Channel PWM                                    |

| - Val              | • UART/HS-UART                                     |

| 20                 | USI (SPI/uWire)                                    |

| Main Function            |

|--------------------------|

| I 2C (Master) Controller |

| Keypad Scan Controller   |

## 32-BIT ARM926EJ-S BASED MCU

### 2. FEATURES

#### Architecture

- Efficient and powerful ARM926EJ-S core with fully 16/32-bit RISC architecture

- Little Endian mode supported

- 8K-byte I-cache and 8K-byte D-cache with MMU

- Cost-effective JTAG-based debug solution

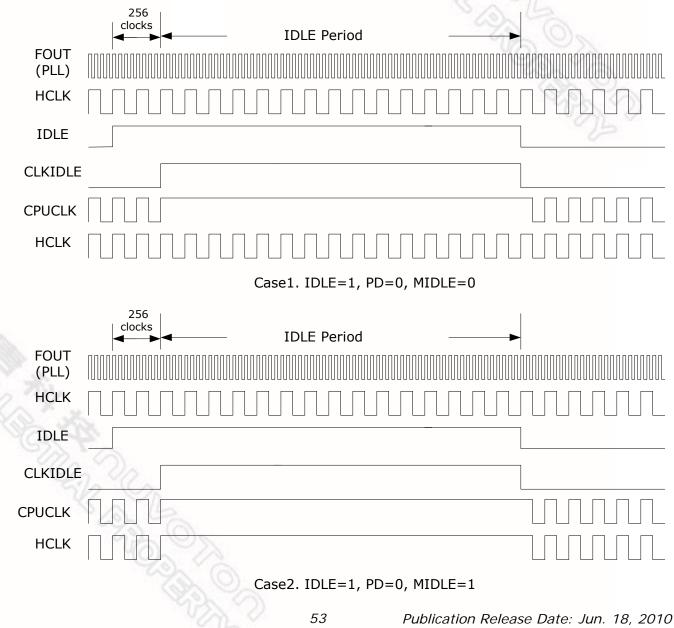

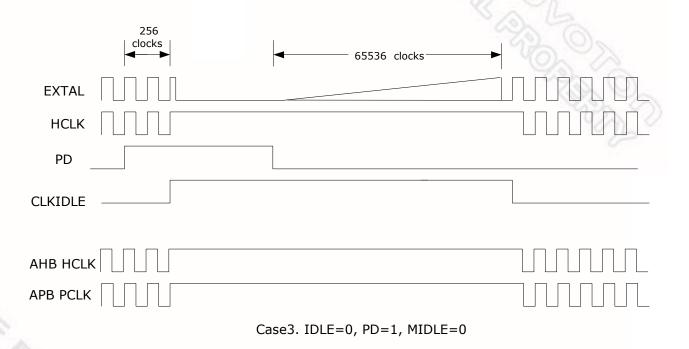

#### Power management

- Programmable clock enable for individual peripherals

- IDLE mode to halt ARM Core and keep peripheral working

- Power-Down mode to stop all clocks included external crystal oscillator.

- Exit IDLE/Power-Down by interrupts

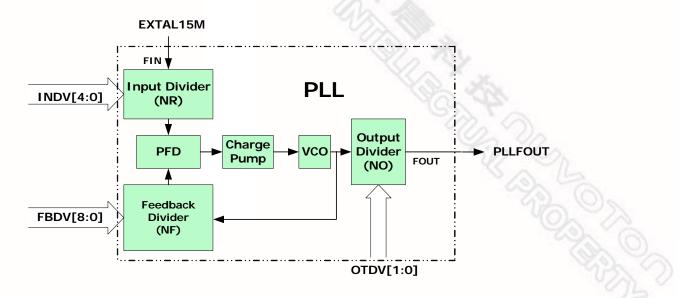

#### PLL

- Supports two on-chip PLLs

- The external clock can be multiplied by on-chip PLL to provide high frequency system clock

- The input frequency range is 4-30MHz; 15MHz is preferred.

- Programmable clock frequency

- Wakeup by interrupt, USB device.

### Advanced Interrupt Controller

- 31 interrupt sources, including 3 external interrupt sources

- Programmable normal or fast interrupt mode (IRQ, FIQ)

- Programmable as either edge-triggered or level-sensitive for 3 external interrupt sources

- Programmable as either low-active or high-active for 3 external interrupt sources

- Priority methodology is encoded to allow for interrupt daisy-chaining

- Automatically mask out the lower priority interrupt during interrupt nesting

- Automatically clear the interrupt flag when the interrupt source is programmed to be edge-triggered

### **General DMA Controller**

• 2-channel General DMA for memory-to-memory data transfers without CPU intervention

### 32-BIT ARM926EJ-S BASED MCU

- Increments or decrements a source or destination address in 8-bit, 16-bit or 32-bit data transfers

- 8-data burst mode

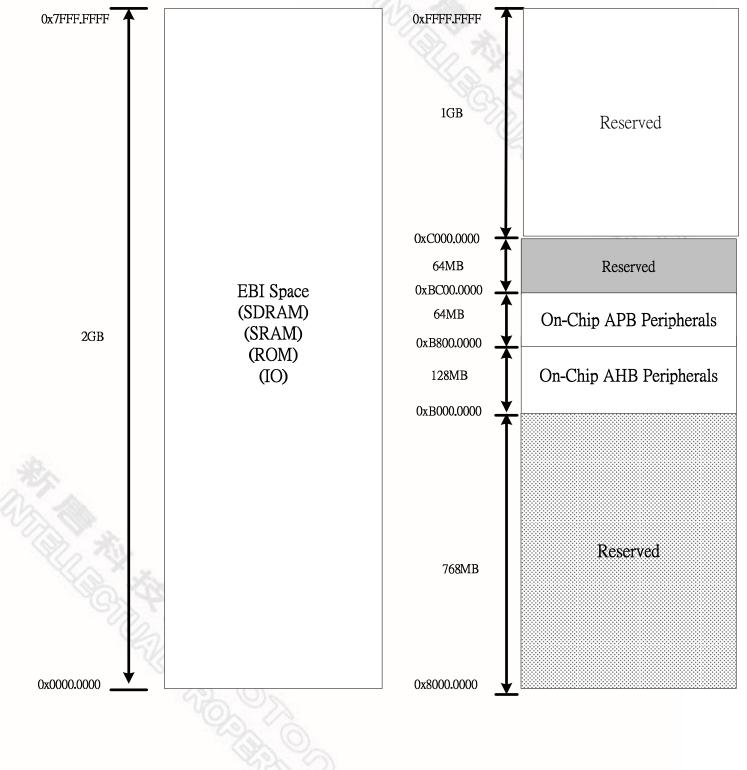

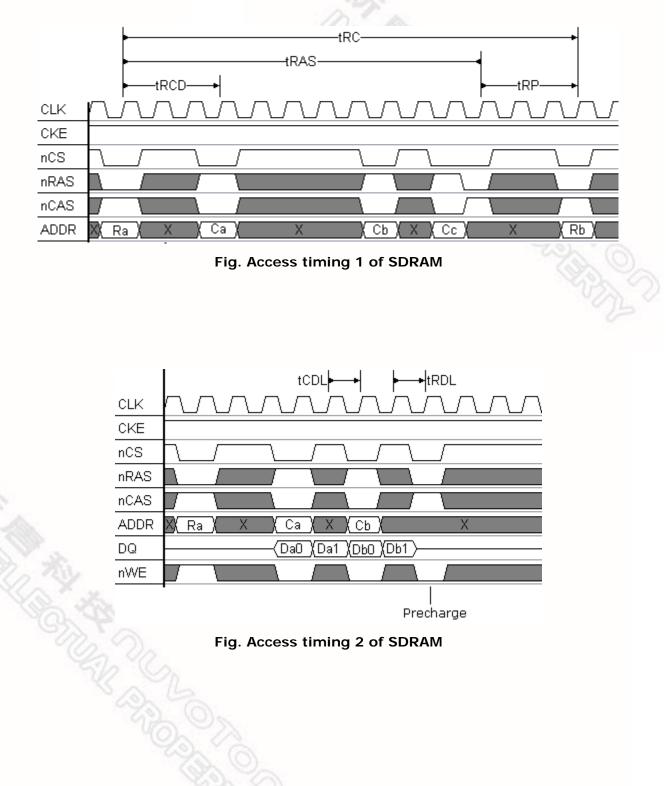

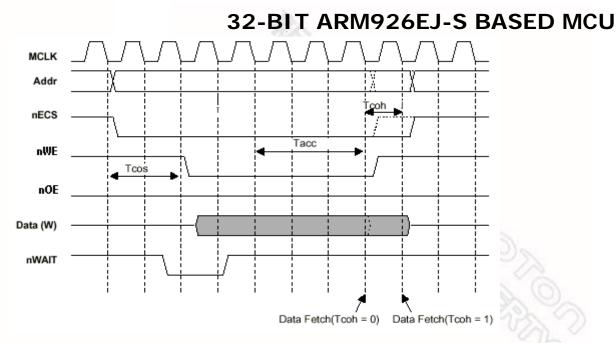

### **External Bus Interface**

- 8/16/32-bit external bus support for ROM/SRAM, flash memory, SDRAM and external I/Os

- Programmable access cycle (0-7 wait cycle)

- Four-word depth write buffer

### **Ethernet MAC Controller**

- 100/10-Mbps operation

- DMA engine with burst mode

- MAC Tx/Rx buffers (256 bytes Tx, 256 bytes Rx)

- Full compliance with IEEE standard 802.3

- RMII interface only

- Station Management Signaling

- On-Chip CAM (up to 16 destination addresses)

- Full-duplex mode with PAUSE feature

- Long/short packet modes

### LCD Controller

- Support the 8/12/16/18-bit data interface to connect with 80/68 series MPU type LCM module

- Convert RGB-565, YUV-422 display data to RGB-444, RGB-565, RGB-666, YUV-422 color format for display output

- Support CCIR-656( with vsync / hsync / data enable sync signal ) 8/16-bit YUV data output format to connect with external TV encoder

- Support 8/16 bpp OSD data with image overlay function to facilitate the diverse graphic UI.

- Support linear 1X 8X image scaling up function.

- Support Picture-In-Picture display function

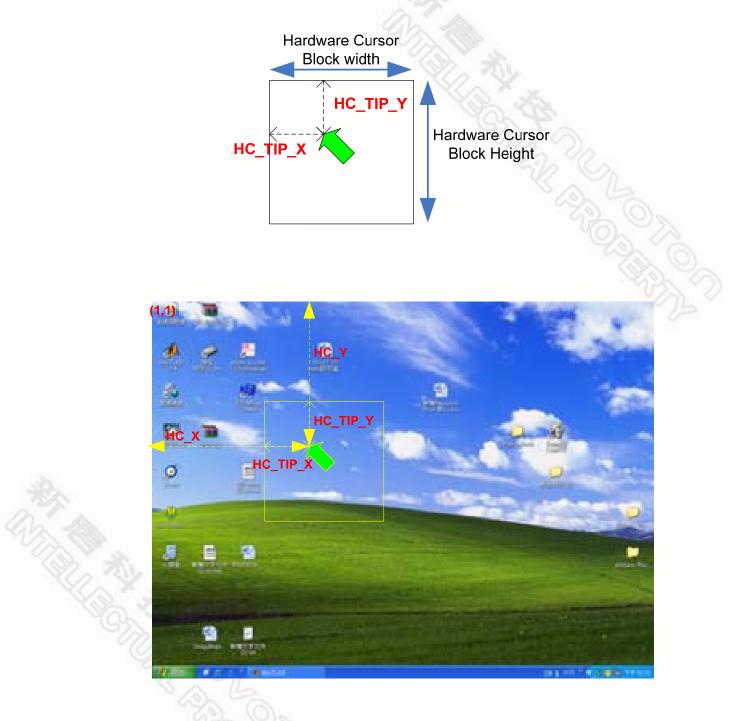

- Support hardware cursor.

### 2-D Graphics Engine

- Color depth 8-bit/16-bit/32-bit in RGB domain or RGB332/RGB565/RGB888 are supported

- Contains 2D Bit Block Transfer (BitBLT) functions as defined in Microsoft GDI. It includes HostBLT, Pattern BLT, Color/Font Expanding BLT, Transparent BLT, Tile BLT, Block Move BLT, Copy File BLT, Color/Font Expansion, and Rectangle Fill, etc.

### 32-BIT ARM926EJ-S BASED MCU

- Supports fore/background colors and all Microsoft 256 ternary raster-operation codes (ROP)

- Clipping window can be defined as inside or outside clipping

- Implements the alpha-blending function for source/destination picture overlaying

- Fast Bresenham line drawing algorithm is used to draw solid/textured lines

- Supports rectangular border or frame drawing

- Supports picture re-sizing by 1/255 ~ 254/255 down-scaling and 1 ~ 1.996 up-scaling (1+254/255).

- Supports object rotations in different degrees, that is L45/L90/R45/R90/M180/F180/X180, where

- ♦ L45/L90 means rotate left 45/90 degrees,

- R45/R90 means rotate right 45/90 degrees,

- M180 means mirror (flop),

- ♦ F180 means up-side-down (flip) and X180 for rotations by 180 degrees

### 2-Channel AC97/I2S Controller

- Support I2S interface.

- Support AC97 interface.

- Built-in an 8x32 bits internal buffer.

- Support DMA function for data transfer between internal buffer and system memory.

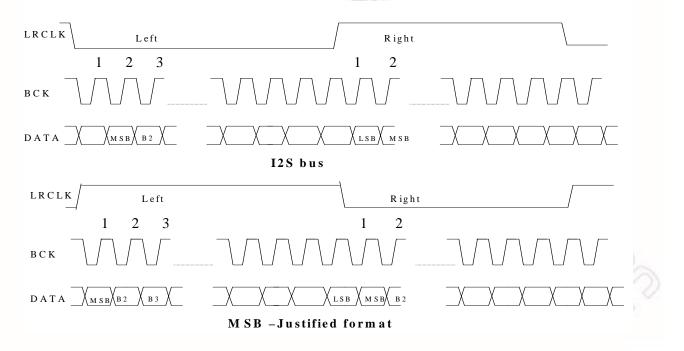

- Support 16-bit I2S and MSB-justified format.

### **USB Host Controller with transceiver**

- Fully compliant with USB Revision 2.0 specification.

- Enhanced Host Controller Interface (EHCI) Revision 1.0 compatible.

- Open Host Controller Interface (OHCI) Revision 1.0 compatible.

- Supports high-speed (480Mbps), full-speed (12Mbps) and low-speed (1.5Mbps) USB devices.

- Supports Control, Bulk, Interrupt, Isochronous and Split transfers.

- Built-in DMA for real-time data transfer.

- Support two ports (one port transceiver is shared with USB Device Controller)

### **USB** Device Controller with transceiver

- Compliant with USB version 2.0 specification.

- Software control for device remote-wakeup.

- Supports 6 configurable IN/OUT endpoints in addition to Control Endpoint. Each of these endpoints can be configures as IN or OUT with Isochronous, Bulk or Interrupt transfer.

- Three different modes of operation of an in-endpoint (Auto validation mode, manual validation mode, Fly mode.

### 32-BIT ARM926EJ-S BASED MCU

• Supports Endpoint Maximum Packet Size up to 1024 bytes.

#### Flash Memory Interface (FMI)

- Directly connect to Secure Digital (SD, MMC and SDIO) flash memory card, Memory Stick (Memory stick PRO) and NAND type flash memory.

- Supports DMA function to accelerate the data transfer between the internal buffer, external SDRAM, and flash memory card.

- Two 512 bytes internal buffers are embedded inside

#### I2C Master

- Compatible with I<sup>2</sup>C standard, support master mode only

- Multi Master Operation

- Clock stretching and wait state generation

- Provide multi-byte transmit operation, up to 4 bytes can be transmitted in a single transfer

- Software programmable acknowledge bit

- Arbitration lost interrupt, with automatic transfer cancellation

- Start/Stop/Repeated Start/Acknowledge generation

- Start/Stop/Repeated Start detection

- Bus busy detection

- Supports 7 bit addressing mode

- Software mode I<sup>2</sup>C

### Universal Serial Interface (USI)

- Support MICROWIRE/SPI master mode

- Support full/half duplex synchronous serial data transfer

- Variable length of transfer word up to 32 bits

- Provide burst mode operation, transmit/receive can be executed up to four times in one transfer

- MSB or LSB first data transfer

- Receive and Transmit on both rising or falling edge of serial clock independently

#### UART

- Three UART (serial I/O) blocks with interrupt-based operation

- Support for 5-bit, 6-bit, 7-bit or 8-bit serial data transmit and receive

- Programmable baud rates

- 1,1<sup>1</sup>/<sub>2</sub> or 2 stop bits

### 32-BIT ARM926EJ-S BASED MCU

- Odd or even parity

- Break generation and detection

- Parity, overrun and framing error detection

- X16 clock mode

- Support for IrDA and two debug ports

#### Timers

- Five programmable 24-bit timers with 8-bit pre-scalar

- One programmable 20-bit Watchdog timer

- One-short mode, period mode or toggle mode operation

#### 4-Channel PWM

- Four 16-bit timers

- Two 8-bit pre-scalars & Two 4-bit divider

- Programmable duty control of output waveform (PWM)

- Auto reload mode or one-shot pulse mode

- Dead-zone generator

### Keypad Scan Interface

- Scan up to 16x8 with an external 4 to 16 decoder; or 4x8 array without auxiliary component

- Programmable de-bounce time

- One or two keys scan with interrupt and three keys reset function.

- Support low power wakeup function

### Programmable I/Os

- Pins individually configurable to input, output or I/O mode for dedicated signals

- I/O ports are Programmable and Configurable for Multiple functions

### **Operation Voltage Range**

- VDD18 for IO Buffer: 1.8V+/-10%

- VDD33 for Core Logic: 3.3V+/-10%

- USBVDDC0/USBVDDC1/USBVDDT0/USBVDDT1 for USB: 3.3V+/-5%

- PLLVDD18 for PLL: 1.8V+/-10%

### 32-BIT ARM926EJ-S BASED MCU

### **Operation Temperature Range**

● -40°C ~+85°C

### **Operating Frequency**

• Up to 200 MHz for ARM926EJ-S CPU

### Package Type

• 216-Pin LQFP, Pb free

32-BIT ARM926EJ-S BASED MCU

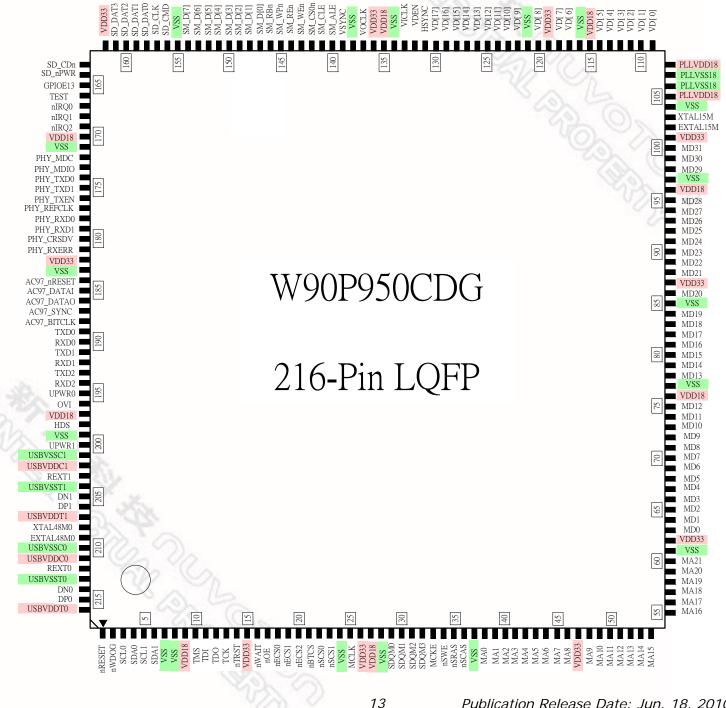

3. PIN DIAGRAM

#### NUC950ADN Pin Diagram

### 32-BIT ARM926EJ-S BASED MCU

#### 4. PIN ASSIGNMENT

#### Table 4.1 NUC950ADN Pins Assignment

| Pad Name               | NUC950ADN                   |  |

|------------------------|-----------------------------|--|

| Clock & Reset          | ( 5 pins )                  |  |

| EXTAL15M               | 102                         |  |

| XTAL15M                | 103                         |  |

| EXTAL48MO              | 209                         |  |

| XTAL48MO               | 208                         |  |

| nRESET                 | 1                           |  |

| TAP Interface          | ( 5 pins )                  |  |

| TMS                    | 10                          |  |

| TDI                    | 11                          |  |

| TDO                    | 12                          |  |

| тск                    | 13                          |  |

| nTRST                  | 14                          |  |

| External Bus Interface | ( 71 pins )                 |  |

| MA [21:0]              | 60-48,46-38                 |  |

| MD [31:0]              | 100-98,95-88,86,84-78,75-63 |  |

| nWBE [3:0] /           | 32-29                       |  |

| SDQM [3:0]             |                             |  |

| nSCS [1:0]             | 23-22                       |  |

| nSRAS                  | 35                          |  |

| nSCAS                  | 36                          |  |

| МСКЕ                   | 33                          |  |

| nSWE                   | 34                          |  |

| MCLK                   | 25                          |  |

| nWAIT                  | 16                          |  |

| nBTCS                  | 21                          |  |

| nECS [2:0]             | 20-18                       |  |

| nOE                    | 17                          |  |

| Pad Name           | NUC950ADN   |

|--------------------|-------------|

| Ethernet Interface | ( 10 pins ) |

| PHY_MDC /          | 172         |

| GPIOF[0]           |             |

| PHY_MDIO /         | 173         |

| GPIOF[1]           |             |

| PHY_TXD [1:0] /    | 175-174     |

| GPIOF[3:2]         |             |

| PHY_TXEN /         | 176         |

| GPIOF[4]           | Sol 4       |

| PHY_REFCLK /       | 177         |

| GPIOF[5]           |             |

| PHY_RXD [1:0] /    | 179-178     |

| GPIOF[7:6]         | (N)         |

| PHY_CRSDV /        | 180         |

| GPIOF[8]           |             |

| PHY_RXERR /        | 181         |

| GPIOF[9]           |             |

| AC97/I2S/PWM       | ( 5 pins )  |

| AC97_nRESET /      | 184         |

| I2S_SYSCLK /       |             |

| - /                |             |

| GPIOG[12]          |             |

| AC97_DATAI /       | 185         |

| 12S_DATAI /        |             |

| PWM [0] /          |             |

| GPIOG[13]          |             |

| AC97_DATAO /       | 186         |

| 12S_DATAO /        |             |

| PWM [1] /          |             |

| GPIOG[14]          |             |

| AC97_SYNC /        | 187         |

| 12S_WS /           |             |

| PWM [2] /          |             |

| GPIOG[15]          |             |

| AC97_BITCLK /      | 188         |

| I2S_BITCLK /       | 25          |

| PWM [3] /          | 1 Parts     |

|                    |             |

| USB Interface    | ( 10 pins ) |

|------------------|-------------|

| DPO              | 215         |

| DNO              | 214         |

| REXTO            | 212         |

| UPWRO            | 195         |

| OVI              | 196         |

| HDS              | 198         |

| DP1              | 206         |

| DN1              | 205         |

| REXT1            | 203         |

| UPWR1            | 200         |

| Pad Name         | NUC950ADN   |

| I2C/USI (SPI/MW) | ( 4 pins )  |

| SCLO /           | 3           |

| SFRM /           |             |

| GPIOG[0]         | 6           |

| SDA0 /           | 4           |

| SSPTXD /         |             |

| GPIOG[1]         |             |

| SCL1 /           | 5           |

| SCLK /           |             |

| GPIOG[2]         |             |

| SDA1 /           | 6           |

| SSPRXD /         |             |

| GPIOG[3]         |             |

| Pad Name         | NUC950ADN   |

| UART             | ( 6 pins )  |

| TXD0 /           | 189         |

| GPIOE[0]         |             |

| RXD0 /           | 190         |

| GPIOE[1]         |             |

| TXD1(B) /        | 191         |

| GPIOE[2]         |             |

| RXD1(B) /        | 192         |

| GPIOE[3]         |             |

| TXD2(IrDA) /     | 193         |

| GPIOE[6]         |             |

| 61102[0]         |             |

| RXD2(IrDA) /     | 194         |

### 32-BIT ARM926EJ-S BASED MCU

| Pad Name           |      | NUC950ADN  |

|--------------------|------|------------|

| SDIO(SD)/          |      | ( 8 pins ) |

| Memory Stick       |      |            |

| SD_CMD /           | 156  |            |

| MS_BS /            |      |            |

| GPIOD[0]           |      |            |

| SD_CLK /           | 157  | -07-63     |

| MS_CLK /           |      |            |

| GPIOD[1]           |      |            |

| SD_DATO /          | 158  | Ser Car    |

| MS_DATO /          |      |            |

| GPIOD[2]           |      |            |

| SD_DAT1 /          | 159  | 292 (0     |

| MS_DAT1 /          |      |            |

| GPIOD[3]           |      |            |

| SD_DAT2 /          | 160  | 2          |

| MS_DAT2 /          |      |            |

| GPIOD[4]           |      |            |

| SD_DAT3 /          | 161  |            |

| MS_DAT3 /          |      |            |

| GPIOD[5]           |      |            |

| SD_CDn /           | 163  |            |

| MS_CDn /           |      |            |

| GPIOD[6]           |      |            |

| SD_nPWR /          | 164  |            |

| MS_nPWR /          |      |            |

| GPIOD[8]           |      |            |

| Pad Name           |      | NUC950ADN  |

| NAND Flash(SM)/KPI |      | ( 15pins ) |

| SM_CS0n /          | 142  |            |

| KPI_ROW[0] /       |      |            |

| GPIOC[0]           |      |            |

| SM_ALE /           | 140  |            |

| KPI_ROW[1]         |      |            |

| GPIOC[1]           | )    |            |

| SM_CLE /           | 141  |            |

| KPI_ROW[2]         | (A)  |            |

| GPIOC[2]           | A Va |            |

17

| SM_WEn /                                                                                                                                                                                                                                    | 143                                                                                                                                                                                                                                                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| KPI_ROW[3]                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                               |

| GPIOC[3]                                                                                                                                                                                                                                    | the second s                                                                                                                                                                                                |

| SM_REn /                                                                                                                                                                                                                                    | 144                                                                                                                                                                                                                                                                                                           |

| GPIOC[4]                                                                                                                                                                                                                                    | AL OCH                                                                                                                                                                                                                                                                                                        |

| SM_WPn /                                                                                                                                                                                                                                    | 145                                                                                                                                                                                                                                                                                                           |

| GPIOC[5]                                                                                                                                                                                                                                    | Sola Sala                                                                                                                                                                                                                                                                                                     |

| SM_RBn /                                                                                                                                                                                                                                    | 146                                                                                                                                                                                                                                                                                                           |

| GPIOC[6]                                                                                                                                                                                                                                    | 50 00                                                                                                                                                                                                                                                                                                         |

| SM_D[7:0] /                                                                                                                                                                                                                                 | 154-147                                                                                                                                                                                                                                                                                                       |

| KPI_COL[7:0] /                                                                                                                                                                                                                              | ~~~ (O)                                                                                                                                                                                                                                                                                                       |

| GPIOC[14:7]                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                               |

| Pad Name                                                                                                                                                                                                                                    | NUC950ADN                                                                                                                                                                                                                                                                                                     |

| LCD                                                                                                                                                                                                                                         | ( 23 pins )                                                                                                                                                                                                                                                                                                   |

| VD [17:0]                                                                                                                                                                                                                                   | 130-122,120,118-117,114-109                                                                                                                                                                                                                                                                                   |

| HSYNC                                                                                                                                                                                                                                       | 131                                                                                                                                                                                                                                                                                                           |

| VSYNC                                                                                                                                                                                                                                       | 139                                                                                                                                                                                                                                                                                                           |

| VDEN                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                               |

| VDEN                                                                                                                                                                                                                                        | 132                                                                                                                                                                                                                                                                                                           |

| VICLK                                                                                                                                                                                                                                       | 132<br>133                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                               |

| VICLK                                                                                                                                                                                                                                       | 133                                                                                                                                                                                                                                                                                                           |

| VICLK<br>VOCLK                                                                                                                                                                                                                              | 133<br>137                                                                                                                                                                                                                                                                                                    |

| VICLK<br>VOCLK<br>Pad Name                                                                                                                                                                                                                  | 133<br>137<br>NUC950ADN                                                                                                                                                                                                                                                                                       |

| VICLK<br>VOCLK<br>Pad Name<br>Miscellaneous                                                                                                                                                                                                 | 133         137         NUC950ADN         ( 6 pins )                                                                                                                                                                                                                                                          |

| VICLK<br>VOCLK<br>Pad Name<br>Miscellaneous<br>nIRQ [2:0] /                                                                                                                                                                                 | 133         137         NUC950ADN         ( 6 pins )                                                                                                                                                                                                                                                          |

| VICLK<br>VOCLK<br>Pad Name<br>Miscellaneous<br>nIRQ [2:0] /<br>GPIOH[2:0]                                                                                                                                                                   | 133         137         NUC950ADN         ( 6 pins )         169-167                                                                                                                                                                                                                                          |

| VICLK<br>VOCLK<br>Pad Name<br>Miscellaneous<br>nIRQ [2:0] /<br>GPIOH[2:0]<br>nWDOG /                                                                                                                                                        | 133         137         NUC950ADN         ( 6 pins )         169-167                                                                                                                                                                                                                                          |

| VICLK<br>VOCLK<br>Pad Name<br>Miscellaneous<br>nIRQ [2:0] /<br>GPIOH[2:0]<br>nWDOG /<br>GPIOI[16]                                                                                                                                           | 133         137         NUC950ADN         ( 6 pins )         169-167         2                                                                                                                                                                                                                                |

| VICLK<br>VOCLK<br>Pad Name<br>Miscellaneous<br>nIRQ [2:0] /<br>GPIOH[2:0]<br>nWDOG /<br>GPIOI[16]<br>GPIOE13                                                                                                                                | 133         137         NUC950ADN         ( 6 pins )         169-167         2         165                                                                                                                                                                                                                    |

| VICLK<br>VOCLK<br>Pad Name<br>Miscellaneous<br>nIRQ [2:0] /<br>GPIOH[2:0]<br>nWDOG /<br>GPIOI[16]<br>GPIOE13<br>TEST                                                                                                                        | 133         137         NUC950ADN         ( 6 pins )         169-167         2         165         166                                                                                                                                                                                                        |

| VICLK<br>VOCLK<br>Pad Name<br>Miscellaneous<br>nIRQ [2:0] /<br>GPIOH[2:0]<br>nWDOG /<br>GPIOI[16]<br>GPIOE13<br>TEST<br>Power/Ground                                                                                                        | 133         137         NUC950ADN         ( 6 pins )         169-167         2         165         166         (48 pins)                                                                                                                                                                                      |

| VICLK<br>VOCLK<br>Pad Name<br>Miscellaneous<br>nIRQ [2:0] /<br>GPIOH[2:0]<br>nWDOG /<br>GPIOI[16]<br>GPIOE13<br>TEST<br>Power/Ground<br>VDD18                                                                                               | 133         137         NUC950ADN         ( 6 pins )         169-167         2         165         166         (48 pins)         9,27,76,96,115,135,170,197         15,26,47,62,87,101,119,136,162,182                                                                                                        |

| VICLK<br>VOCLK<br>Pad Name<br>Miscellaneous<br>nIRQ [2:0] /<br>GPIOH[2:0]<br>nWDOG /<br>GPIOI[16]<br>GPIOE13<br>TEST<br>Power/Ground<br>VDD18<br>VDD33                                                                                      | 133         137         NUC950ADN         ( 6 pins )         169-167         2         165         166         (48 pins)         9,27,76,96,115,135,170,197         15,26,47,62,87,101,119,136,162,182                                                                                                        |

| VICLK<br>VOCLK<br>Pad Name<br>Miscellaneous<br>nIRQ [2:0] /<br>GPIOH[2:0]<br>nWDOG /<br>GPIOI[16]<br>GPIOE13<br>TEST<br>Power/Ground<br>VDD18<br>VDD33<br>VSS                                                                               | 133         137         NUC950ADN         ( 6 pins )         169-167         2         165         166         (48 pins)         9,27,76,96,115,135,170,197         15,26,47,62,87,101,119,136,162,182         7,8,24,28,37,61,77,85,97,104,116,121,134,138,155,171,183,1                                     |

| VICLK<br>VOCLK<br>Pad Name<br>Miscellaneous<br>nIRQ [2:0] /<br>GPIOH[2:0]<br>nWDOG /<br>GPIOI[16]<br>GPIOE13<br>TEST<br>Power/Ground<br>VDD18<br>VDD18<br>VDD33<br>VSS<br>USBVDDC0 (3.3V)                                                   | 133         137         NUC950ADN         ( 6 pins )         169-167         2         165         166         (48 pins)         9,27,76,96,115,135,170,197         15,26,47,62,87,101,119,136,162,182         7,8,24,28,37,61,77,85,97,104,116,121,134,138,155,171,183,1         211                         |

| VICLK<br>VOCLK<br>Pad Name<br>Miscellaneous<br>nIRQ [2:0] /<br>GPIOH[2:0]<br>nWDOG /<br>GPIOI[16]<br>GPIOE13<br>TEST<br>Power/Ground<br>VDD18<br>VDD33<br>VSS<br>USBVDDC0 (3.3V)<br>USBVSSC0                                                | 133         137         NUC950ADN         ( 6 pins )         169-167         2         165         166         (48 pins)         9,27,76,96,115,135,170,197         15,26,47,62,87,101,119,136,162,182         7,8,24,28,37,61,77,85,97,104,116,121,134,138,155,171,183,1         211         210             |

| VICLK<br>VOCLK<br>Pad Name<br>Miscellaneous<br>nIRQ [2:0] /<br>GPIOH[2:0]<br>nWDOG /<br>GPIOI[16]<br>GPIOI[16]<br>GPIOE13<br>TEST<br>Power/Ground<br>VDD18<br>VDD18<br>VDD33<br>VSS<br>USBVDDC0 (3.3V)<br>USBVSSC0<br>USBVDDT0 (3.3V)       | 133         137         NUC950ADN         ( 6 pins )         169-167         2         165         166         (48 pins)         9,27,76,96,115,135,170,197         15,26,47,62,87,101,119,136,162,182         7,8,24,28,37,61,77,85,97,104,116,121,134,138,155,171,183,1         211         210         216 |

| VICLK<br>VOCLK<br>Pad Name<br>Miscellaneous<br>nIRQ [2:0] /<br>GPIOH[2:0]<br>nWDOG /<br>GPIOI[16]<br>GPIOE13<br>TEST<br>Power/Ground<br>VDD18<br>VDD18<br>VDD33<br>VSS<br>USBVDDC0 (3.3V)<br>USBVDDC0 (3.3V)<br>USBVSSC0<br>USBVDDT0 (3.3V) | 133         137         NUC950ADN         ( 6 pins )         169-167         2         165         166         (48 pins)         9,27,76,96,115,135,170,197         15,26,47,62,87,101,119,136,162,182         7,8,24,28,37,61,77,85,97,104,116,121,134,138,155,171,183,1         211         210         213 |

| USBVSST1 | 204     |

|----------|---------|

| PLLVDD18 | 108,105 |

| PLLVSS   | 107,106 |

### 32-BIT ARM926EJ-S BASED MCU

### 5. PIN DESCRIPTION

### 5.1 Pin Description for Interface

| Pin Name            | ІО Туре    | Description                                               |

|---------------------|------------|-----------------------------------------------------------|

| Clock & Reset (5)   |            |                                                           |

| EXTAL15M            | I          | 15MHz External Clock / Crystal Input for PLL              |

| XTAL15M             | 0          | 15MHz Crystal Output                                      |

| EXTAL48MO           | 0          | 48MHz Crystal Output for USB2.0 PHY                       |

| XTAL48MO            | I          | 48MHz Crystal Input for USB2.0 PHY                        |

| nRESET              | I          | System Reset (Low active)                                 |

| TAP Interface (5)   |            |                                                           |

| тск                 | ID         | JTAG Test Clock, internal pull-down                       |

| TMS                 | IU         | JTAG Test Mode Select, internal pull-up                   |

| TDI                 | IU         | JTAG Test Data in, internal pull-up                       |

| TDO                 | 0          | JTAG Test Data out                                        |

| nTRST               | IU         | JTAG Reset, active-low, internal pull-up                  |

| External Bus Interf | ace (72)   |                                                           |

| MA [21:0]           | 0          | Address Bus of external memory and IO devices.            |

|                     |            | (MA[21:13] are set to input mode when nRESET low active)  |

| MD [31:0]           | 10 (D)     | Data Bus of external memory and IO device                 |

|                     |            | (Pull-down are programmable)                              |

| nWBE [3:0] /        | 0          | Write Byte Enable for specific device (nECS [2:0]).       |

| SDQM [3:0]          |            | Data Bus Mask signal for SDRAM (nSCS [1:0]), (Low active) |

| nSCS [1:0]          | 0          | SDRAM chip select for two external banks, (Low active)    |

| nSRAS               | 0          | Row Address Strobe for SDRAM, (Low active)                |

| nSCAS               | 0          | Column Address Strobe for SDRAM, (Low active)             |

| nSWE                | 0          | SDRAM Write Enable, (Low active)                          |

| MCKE                | 0          | SDRAM Clock Enable                                        |

| MCLK                | 0          | System Master Clock Out, SDRAM clock                      |

| nWAIT               | 0100       | External Wait, (Low active), internal pull-up             |

| nBTCS               | 0          | ROM/Flash Chip Select, (Low active)                       |

| nECS [2:0]          | 0          | External I/O Chip Select, (Low active)                    |

| nOE                 | 0          | ROM/Flash, External Memory Output Enable, (Low active)    |

| Ethernet RMII Inte  | rface (10) |                                                           |

| PHY_MDC             | 0(IS)      | RMII Management Data Clock                                |

|                     |            |                                                           |

| Pin Name                | ІО Туре | Description                               |

|-------------------------|---------|-------------------------------------------|

| PHY_MDIO                | 10(D)   | RMII Management Data I/O                  |

|                         |         | (Pull-down is programmable)               |

| PHY_TXD [1:0]           | 0(IU)   | RMII Transmit Data bus                    |

|                         |         | (Pull-up are programmable)                |

| PHY_TXEN                | O(ID)   | RMII Transmit Enable                      |

|                         |         | (Pull-down is programmable)               |

| PHY_REFCLK              | O(ID)   | RMII Reference Clock.                     |

|                         |         | (Pull-down is programmable)               |

| PHY_RXD [1:0]           | I (OU)  | RMII Receive Data bus                     |

|                         |         | (Pull-up are programmable)                |

| PHY_CRSDV               | I (OD)  | RMII Carrier Sense / Receive Data Valid   |

|                         |         | (Pull-down is programmable)               |

| PHY_RXERR               | I (OD)  | RMII Receive Data Error                   |

|                         |         | (Pull-down is programmable)               |

| AC97/12S/PWM (5)        |         |                                           |

| AC97_nRESET /           | O(ID)   | AC97 Controller RESET Output.             |

| I2S_SYSCLK              |         | I2S Controller System Clock Output.       |

|                         |         | (Pull-down is programmable)               |

| AC97_DATAI /            | 10(D)   | AC97 Controller Data Input.               |

| 12S_DATAI /             |         | 12S Controller Data Input.                |

| PWM [0]                 |         | PWM Channel 0 Output.                     |

|                         |         | (Pull-down is programmable)               |

| AC97_DATAO /            | O(ID)   | AC97 Controller Data Output.              |

| 12S_DATAO /             |         | I2S Controller Data Output.               |

| PWM [1]                 |         | PWM Channel 1 Output.                     |

|                         |         | (Pull-down is programmable)               |

| AC97_SYNC /             | IO(D)   | AC97 Controller Synchronous Pulse Output. |

| 12S_WS /                |         | I2S Controller Word Select.               |

| PWM [2]                 | 5       | PWM Channel 2 Output.                     |

|                         | -21     | (Pull-down is programmable)               |

| AC97_BITCLK /           | IOSD    | AC97 Controller Bit Clock Input.          |

| I2S_BITCLK /<br>PWM [3] | 200     | I2S Controller Bit Clock.                 |

|                         | ne      | PWM Channel 3 Output.                     |

|                         | 10 COL  | (Pull-down with Schmitt trigger input )   |

| USB Interface (10)      |         |                                           |

| DPO                     | 10      | Differential Positive USB Port0 IO signal |

| DNO                     | 10      | Differential Negative USB Port0 IO signal |

| REXTO                   | Α       | External Resister Connect for PortO       |

## 32-BIT ARM926EJ-S BASED MCU

| Pin Name        | ІО Туре                                 | Description                                                                                   |

|-----------------|-----------------------------------------|-----------------------------------------------------------------------------------------------|

| DP1             | 10                                      | Differential Positive USB Port1 IO signal                                                     |

| DN1             | 10                                      | Differential Negative USB Port1 IO signal                                                     |

| REXT1           | Α                                       | External Resister Connect for Port1                                                           |

| UPWR1           | 0                                       | USB Port1 Power Control signal                                                                |

| ονι             | I                                       | USB Over Current Detection signal                                                             |

| HDS             | I                                       | USB PHY 0 Device/Host Mode Select Control signal                                              |

| UPWR0           | 0                                       | USB Port0 Power Control signal                                                                |

|                 |                                         | This pin is always driven to Low when USB Port0 is at Device mode (the HDS pin at high state) |

| 2C/USI (SPI/MW) | ) Interface (4                          | )                                                                                             |

| SCLO /          | IOS                                     | I 2C Serial Clock Line 0.                                                                     |

| SFRM            |                                         | USI Serial Frame.                                                                             |

|                 |                                         | (Input with Schmitt trigger)                                                                  |

| SDA0 /          | 105                                     | 12C Serial Data Line 0.                                                                       |

| SSPTXD          |                                         | USI Serial Transmit Data.                                                                     |

|                 |                                         | (Input with Schmitt trigger)                                                                  |

| SCL1 /          | IOS                                     | I 2C Serial Clock Line 1.                                                                     |

| SCLK            |                                         | USI Serial Clock.                                                                             |

|                 |                                         | (Input with Schmitt trigger)                                                                  |

| SDA1 /          | IOS                                     | I 2C Serial Data Line 1.                                                                      |

| SSPRXD          |                                         | USI Serial Receive Data.                                                                      |

|                 |                                         | (Input with Schmitt trigger)                                                                  |

| JARTO/UART1/UA  | ART2 Interfac                           | e (6)                                                                                         |

| TXDO            | 10(D)                                   | UARTO Transmit Data.                                                                          |

|                 |                                         | (Pull-down is programmable)                                                                   |

| RXDO            | IO(D)                                   | UARTO Receive Data.                                                                           |

|                 |                                         | (Pull-down is programmable)                                                                   |

| TXD1            | IO(D)                                   | UART1 Transmit Data                                                                           |

|                 | 32                                      | (Pull-down is programmable)                                                                   |

| RXD1            | IO(D)                                   | UART1 Receive Data                                                                            |

|                 |                                         | (Pull-down is programmable)                                                                   |

| TXD2(IrDA)      | 10(D)                                   | UART2 Transmit Data supporting SIR IrDA.                                                      |

|                 | 200                                     | (Pull-down is programmable)                                                                   |

| RXD2(IrDA)      | 10(D)                                   | UART2 Receive Data supporting SIR IrDA.                                                       |

|                 | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ | (Pull-down is programmable)                                                                   |

22

and a

| Pin Name                                  | ІО Туре  | Description                                          |

|-------------------------------------------|----------|------------------------------------------------------|

| SDO_CMD /                                 | 10(U)    | SD/SDIO Mode – Command/Response (SPI Mode – Data In) |

| MSO_BS                                    |          | Memory Stick Mode – Bus State.                       |

|                                           |          | (Pull-up is programmable)                            |

| SDO_CLK /                                 | 10(U)    | SD/SDIO Mode – Clock; (SPI Mode – Clock)             |

| MSO_CLK                                   |          | Memory Stick Mode – Clock                            |

|                                           |          | (Pull-up is programmable)                            |

| SDO_DATO /                                | 10(U)    | SD/SDIO Mode – Data Line Bit 0;                      |

| MSO_DATO                                  |          | Memory Stick Mode – Data Line Bit 0;                 |

|                                           |          | (Pull-up is programmable)                            |

| SD0_DAT1 /                                | 10(U)    | SD/SDIO Mode – Data Line Bit 1;                      |

| MS0_DAT1                                  |          | Memory Stick Mode – Data Line Bit 1;                 |

|                                           |          | (Pull-up is programmable)                            |

| SDO_DAT2 /                                | 10(U)    | SD/SDIO Mode – Data Line Bit 2;                      |

| MS0_DAT2                                  |          | Memory Stick Mode – Data Line Bit 2;                 |

|                                           |          | (Pull-up is programmable)                            |

| SDO_DAT3 /                                | 10(U)    | SD/SDIO Mode – Data Line Bit 3;                      |

| MSO_DAT3                                  |          | Memory Stick Mode – Data Line Bit 3;                 |

|                                           |          | (Pull-up is programmable)                            |

| SD0_CDn /                                 | 10(U)    | SD/SDIO Mode – Card Detect.                          |

| MS0_CDn                                   |          | Memory Stick Mode – Card Detect.                     |

|                                           |          | (Pull-up is programmable)                            |

| SD_nPWR                                   | 10(U)    | SD/SDIO Power FET Control Signal Output.             |

| 1. C. |          | (Pull-up is programmable)                            |

| NAND Flash Interfa                        | ace (15) |                                                      |

| SM_CS0n                                   | O(IU)    | NAND Flash Chip Select #0                            |

| 9022                                      |          | (Pull-up is programmable)                            |

| SM_ALE                                    | O(IU)    | NAND Flash Address Latch Enable                      |

| YO WY                                     |          | (Pull-up is programmable)                            |

| SM_CLE                                    | O(IU)    | NAND Flash Command Latch Enable                      |

| Mar                                       | 21       | (Pull-up is programmable)                            |

| SM_WEn                                    | O(IU)    | NAND Flash Write Enable (Low active)                 |

| Q                                         | 20 40    | (Pull-up is programmable)                            |

| SM_REn                                    | 0(IU)    | NAND Flash Read Enable (Low active)                  |

|                                           | No.      | (Pull-up is programmable)                            |

| SM_WPn                                    | 0(IU)    | NAND Flash Write Protect (Low active)                |

|                                           | R        | (Pull-up is programmable)                            |

| SM_RBn                                    | I (OU)   | NAND Flash Busy (Low active)                         |

|                                           |          | (Pull-up is programmable)                            |

| Pin Name            | ІО Туре  | Description                                                                  |

|---------------------|----------|------------------------------------------------------------------------------|

| SM_D[7:0]           | 10(U)    | NAND Flash Data Bus                                                          |

|                     |          | (Pull-up is programmable)                                                    |

| Keypad Interface (K | PI) (12) |                                                                              |

| KPI_COL[7:0]        | I        | Keypad Column Scan Input Bus                                                 |

|                     |          | This bus is shared with NAND Flash Interface, which is programmable setting. |

| KPI_ROW[3:0]        | 0        | Keypad Row Scan Output Bus                                                   |

|                     |          | This bus is shared with NAND Flash Interface, which is programmable setting. |

| LCD Interface (23)  | -        |                                                                              |

| VD [17:0]           | 0(IU)    | LCD Pixel Data Output.                                                       |

|                     |          | (Pull-up is programmable)                                                    |

| HSYNC               | 0        | Horizontal Sync or Line Sync.                                                |

| VSYNC               | 0        | Vertical Sync or Frame Sync.                                                 |

| VDEN                | 0        | Data Enable or Display Control Signal.                                       |

| VOCLK               | 0        | Pixel Clock Output.                                                          |

| VICLK               | IU       | Pixel Clock Input.                                                           |

| Miscellaneous(6)    |          |                                                                              |

| nIRQ[2:0]           | I (OU)   | External Interrupt Request                                                   |

|                     |          | (Pull-up is programmable)                                                    |

| nWDOG               | 0        | Watchdog Timer Timeout Flag (Low active)                                     |

| GPI OE13            | 10(U)    | Bit 13 of the GPIOE port                                                     |

| TEST                | I        | Test Mode                                                                    |

|                     |          | This pin has to pull low in normal operation.                                |

| Power/Ground        |          |                                                                              |

| VDD18               | Р        | Core Logic power (1.8V)                                                      |

| VDD33               | Р        | IO Buffer power (3.3V)                                                       |

| VSS                 | G        | IO Buffer and Core ground (OV)                                               |

| USBVDDCO            | Р        | USB Port0 PHY power (3.3V)                                                   |

| USBVSSCO            | G        | USB Port0 PHY ground (0V)                                                    |

| USBVDDTO            | P        | USB Port0 PHY Transceiver power (3.3V)                                       |

| USBVSSTO            | G        | USB Port0 PHY Transceiver ground (0V)                                        |

| USBVDDC1            | ₽ V      | USB Port1 PHY power (3.3V)                                                   |

| USBVSSC1            | G        | USB Port1 PHY ground (0V)                                                    |

| USBVDDT1            | P        | USB Port1 PHY Transceiver power (3.3V)                                       |

| USBVSST1            | G        | USB Port1 PHY Transceiver ground (OV)                                        |

| PLLVDD18            | Р        | PLL power (1.8V)                                                             |

| PLLVSS18            | G        | PLL ground (0V)                                                              |

### 32-BIT ARM926EJ-S BASED MCU

### 5.2 GPIO Share Pin Description

In this chip, there are GPIOC $\sim$ GPIOH groups for general IO control. All of GPIO pins are shared with the other interface and define as the following

| GPIO Group                              | Shared pin function    |   |

|-----------------------------------------|------------------------|---|

| GPIOC (15 pins)                         | NAND Flash Interface / |   |

|                                         | КРІ                    |   |

| GPIOC[0]                                | SM_CS0n /              | 6 |

|                                         | KPI_ROW[0]             |   |

| GPIOC[1]                                | SM_ALE /               | 3 |

|                                         | KPI_ROW[1]             | % |

| GPIOC[2]                                | SM_CLE /               |   |

|                                         | KPI_ROW[2]             |   |

| GPIOC[3]                                | SM_WEn /               |   |

|                                         | KPI_ROW[3]             |   |

| GPIOC[4]                                | SM_REn                 |   |

| GPIOC[5]                                | SM_WPn                 |   |

| GPIOC[6]                                | SM_RBn                 |   |

| GPIOC[7]                                | SM_D[0] /              |   |

|                                         | KPI_COL[0]             |   |

| GPIOC[8]                                | SM_D[1] /              |   |

|                                         | KPI_COL[1]             |   |

| GPIOC[9]                                | SM_D[2] /              |   |

|                                         | KPI_COL[2]             |   |

| GPIOC[10]                               | SM_D[3] /              |   |

|                                         | KPI_COL[3]             |   |

| GPIOC[11]                               | SM_D[4] /              |   |

| A MARINA                                | KPI_COL[4]             |   |

| GPIOC[12]                               | SM_D[5] /              |   |

| 5225                                    | KPI_COL[5]             |   |

| GPIOC[13]                               | SM_D[6] /              |   |

| 50 0                                    | KPI_COL[6]             |   |

| GPIOC[14]                               | SM_D[7] /              |   |

| ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ | KPI_COL[7]             |   |

| GPIOD (8 pins) | SD(SDIO) /             |                           |

|----------------|------------------------|---------------------------|

|                | Memory Stick Interface |                           |

|                | 25                     | Publication Poloaso Dato: |

| GPIOD[0] | SD_CMD /  |

|----------|-----------|

|          | MS_BS     |

| GPIOD[1] | SD_CLK /  |

|          | MS_CLK    |

| GPIOD[2] | SD_DATO / |

|          | MS_DATO   |

| GPIOD[3] | SD_DAT1 / |

|          | MS_DAT1   |

| GPIOD[4] | SD_DAT2 / |

|          | MS_DAT2   |

| GPIOD[5] | SD_DAT3 / |

|          | MS_DAT3   |

| GPIOD[6] | SD_CDn /  |

|          | MS_CDn    |

| GPIOD[8] | SD_nPWR / |

|          | MS_nPWR   |

| GPIOE (7 pins) | UART Interface |

|----------------|----------------|

| GPIOE[0]       | TXDO           |

| GPIOE[1]       | RXDO           |

| GPIOE[2]       | TXD1           |

| GPIOE[3]       | RXD1           |

| GPIOE[6]       | TXD2(IrDA)     |

| GPIOE[7]       | RXD2(IrDA)     |

| GPIOE[13]      | GPIOE13        |

| GPIOF (10 pins) | RMII Interface |

|-----------------|----------------|

| GPIOF [0]       | PHY_MDC        |

| GPIOF [1]       | PHY_MDIO       |

| GPIOF [3:2]     | PHY_TXD [1:0]  |

| GPIOF [4]       | PHY_TXEN       |

| GPI OF [5]      | PHY_REFCLK     |

| GPIOF [7:6]     | PHY_RXD [1:0]  |

| GPIOF [8]       | PHY_CRSDV      |

| GPIOF [9]       | PHY_RXERR      |

| GPIOG (9 pins) | I2C/USI                |

|----------------|------------------------|